Varför och hur man använder FPGA:er från Efinix för bildhantering med AI/ML - del 1: Komma igång

Bidraget med av DigiKeys europeiska redaktörer

2023-04-20

Redaktörens anmärkning: Nya tillvägagångssätt för FPGA-arkitekturer ger en mer detaljerad styrning och en större flexibilitet för att tillgodose behoven för ML (maskininlärning) och AI (artificiell intelligens). Den första delen i denna tvådelade serie presenterar en sådan arkitektur från Efinix och hur man kommer igång med hjälp av ett utvecklingskort. Den andra delen tittar på gränssnittet mellan utvecklingskortet och externa enheter samt kringutrustning, som t.ex. en kamera.

Tillämpningar med FPGA:er spelar en mycket viktig roll i industriell styrning, säkerhet och robotteknik samt inom flyg- och fordonsindustrin. Det är tack vare flexibiliteten hos den programmerbara logikkärnan och dess många gränssnittsfunktioner som ett ökande användningsområde för FPGA vid bildbehandling noteras när ML-slutsatser ska användas. FPGA:er är perfekta för implementation i lösningar som har flera kameragränssnitt med hög hastighet. FPGA:er gör det dessutom möjligt att implementera dedikerade bearbetningspipelines i logiken, vilket eliminerar flaskhalsar som skulle vara förknippade med CPU-eller GPU-baserade lösningar.

För många utvecklare, kräver dock tillämpningarna en utökad ML-/AI-funktionalitet och mer detaljerad styrning eller routning och logik, utöver vad klassiska FPGA-arkitekturer med konfigurerbara logikblock (CLB) kan erbjuda. Senare tillvägagångssätt för FPGA-arkitekturer tar itu med dessa problem. Arkitekturen Quantum från Efinix använder exempelvis ett XLR-block (eXchangeable Logic and Routing).

Artikeln diskuterar de viktigaste funktionerna och egenskaperna hos Efinix FPGA-arkitektur, med tonvikt på funktionerna för ML/AI och presenterar faktiska implementeringar. Därefter diskuteras ett utvecklingskort med tillhörande verktyg som utvecklare kan använda för att snabbt komma igång med nästa AI-/ML-bildkonstruktion.

FPGA-enheter från Efinix

Efinix erbjuder för närvarande två produktfamiljer. Företaget introducerade först familjen Trion, med en logiktäthet från 4 000 till 120 000 logiska element (LE) som tillverkas med hjälp av en SMIC 40LL-process. Det senaste sortimentet av enheter i familjen Titanium, har en logiktäthet från 35 000 till 1 000 000 logiska element och tillverkas på den mycket populära 16 nm-noden från TSMC.

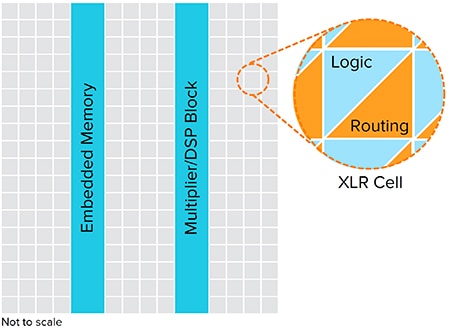

Båda produkterna är baserade på Quantum-arkitekturn, något som är unikt i FPGA-världen. Standardarkitekturen för FPGA bygger på CLB:er som i sin enklaste form innehåller en uppslagstabell (LUT) och vippor. Logiska ekvationer implementeras i CLB:erna som sedan kopplas samman via routning. Quantum-arkitekturen från Efinix rör sig bort från distinkta logik- och routningblock med XLR-blocket.

Det som gör ett XLR-block unikt är att det kan konfigureras för att fungera som en logisk cell med en uppslagstabell, ett register och adderare eller en routningmatris. Tillvägagångssättet ger en mer detaljerad arkitektur som ger flexibel routning, vilket gör det möjligt att uppnå önskad prestanda i implementationer med tung logik eller routning.

Figur 1: Vad som gör ett XLR-block unikt är att det kan konfigureras för att fungera som antingen en logisk cell med en uppslagstabell, ett register och en adderare eller en matris för routning. (Bildkälla: Efinix)

Figur 1: Vad som gör ett XLR-block unikt är att det kan konfigureras för att fungera som antingen en logisk cell med en uppslagstabell, ett register och en adderare eller en matris för routning. (Bildkälla: Efinix)

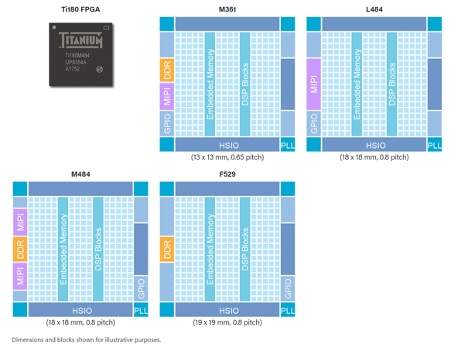

Titanium-enheterna, som är den senaste familjen i sortimentet, har de mest avancerade funktionerna för utvecklaren (figur 2). Tillsammans med XLR-kärnan levererar de seriella multigigabit-länkar som fungerar med antingen 16 eller 25,8 Gbit/s, beroende på vilken enhet som väljs. Multigigabit-länkarna är avgörande för att möjliggöra dataöverföring med höga hastigheter i och utanför kretsen.

Figur 2: Titanium-enheten FPGA Ti180 finns i en mängd olika utföranden beroende på kraven bussbredd, in-och utgångar och minne. (Bildkälla: Efinix)

Figur 2: Titanium-enheten FPGA Ti180 finns i en mängd olika utföranden beroende på kraven bussbredd, in-och utgångar och minne. (Bildkälla: Efinix)

Titanium-enheterna har även ett stort utbud av I/O-gränssnitt som kan grupperas som GPIO (I/O för allmänna ändamål) och kan stödja enkelbalanserade I/O-standarder som t.ex. CMOS med låg spänning (LVCMOS) på 3,3, 2,5 och 1,8 V.

För höghastighets- och differentialgränssnitt har Titanium-enheterna HSIO (high-speed I/O) som stöder obalanserade I/O-standarder som t.ex. LVCMOS vid 1,2 och 1,5 V samt SSTL och HSTL. Differentiella I/O-standarder som stöds av HSIO inkluderar LVDS (Low Voltage Differential Signaling), differentiell SSTL samt HSTL.

Moderna FPGA:er kräver även tätt sammankopplade minnen med hög bandbredd som används för att lagra bildrutor i tillämpningar för bildbehandling, samplingsdata för signalbehandling samt naturligtvis för att köra operativsystem och programvara för processorer som implementerats i FPGA:n. Enheterna i Titanium-serien möjliggör gränssnitt för DDR4 och LPDDR4(x). Beroende på den faktiska Titanium-enhet som valts är busstödet x32 (J) eller x16 (M), medan vissa enheter inte har något stöd för LPDDR4 (L).

FPGA:er i Titanium-familjen är baserade på SRAM och kräver ett konfigurationsminne där enhetskonfigurationen utförs antingen med hjälp av master/slav SPI (Serial Peripheral Interconnect) eller JTAG. För att säkerställa att den här konfigurationsmetoden är säker använder FPGA:n AES GCM-kryptering av bitströmmen tillsammans med AES GCM och RSA-4096 för att tillhandahålla autentisering av bitströmmen. En så stark säkerhet är nödvändig eftersom FPGA:er används i molnkanten där aktörer med skadligt uppsåt kan få tillgång till, och manipulera, deras beteende.

Presentation av utvecklingskortet

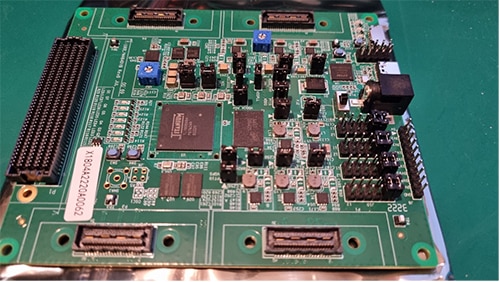

Utvecklingskort utgör en viktig del av utvärderingsprocessen för FPGA:er då de kan användas för att utforska enhetens kapacitet samt prototyptillämpningar, vilket bidrar till att minska den totala risken. Det första utvecklingskortet som finns tillgängligt för att utvärdera FPGA:er från Titanium och för att börja ta fram prototyper är Ti180 M484 (figur 3). Kortet har en FMC-kontakt (FPGA Mezzanine Card) och fyra QSE-kontakter från Samtec.

Figur 3: Tillsammans med en FPGA från Titanium har utvecklingssatsen Ti180 M484 en FMC-kontakt och fyra QSE-kontakter från Samtec. (Bildkälla: Adam Taylor)

Figur 3: Tillsammans med en FPGA från Titanium har utvecklingssatsen Ti180 M484 en FMC-kontakt och fyra QSE-kontakter från Samtec. (Bildkälla: Adam Taylor)

Den FPGA med Ti180 som monterats på utvecklingskortet har 172 000 XLR-celler, 32 globala klockor, 640 digitala signalbehandlingselement (DSP) samt 13 Mbits inbäddat RAM. DSP-elementen möjliggör genomförande av 18 x 19-multiplikationer med fast decimalpunkt och multiplikationer med 48-bitar. Denna DSP kan även optimeras för SIMD-drift (single instruction, multiple data) som körs i antingen en dubbel eller fyrdubbel konfiguration. DSP-element kan även konfigureras för att utföra flyttalsoperationer.

Som de flesta utvecklingskort innehåller Ti180 enkla lysdioder och knappar. Den verkliga styrkan ligger dock i dess gränssnittsmöjligheter. Utvecklingskortet Ti180 har en FMC-kontakt med lågt stiftantal som gör det möjligt att ansluta en stor mängd kringutrustning. Eftersom det är en allmänt vedertagen standard finns det många FMC-kort som gör det möjligt att koppla ihop analog-till-digitalomvandlare (ADC) med hög hastighet, digital-till-analogomvandlare (DAC), nätverk samt minnes- och lagringslösningar.

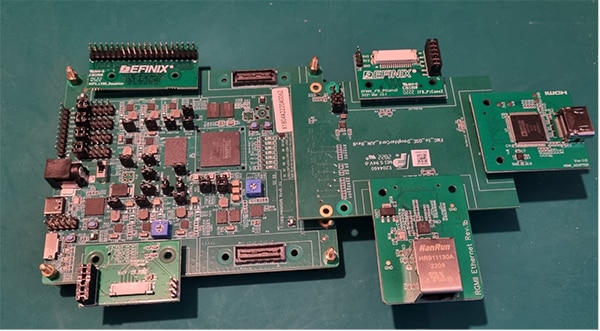

Utöver FMC-anslutningen har kortet fyra QSE-kontakter från Samtec som gör det möjligt för utvecklaren att lägga till expansionskort. QSE-kontakterna används för att tillhandahålla in- och -utgångar för MIPI, där respektive QSE-kontakt tillhandahåller antingen en MIPI-in eller utgång.

Figur 4: Utvecklingssatsen Ti180 M484 visas med sitt mångsidiga utbud av expansionsmöjligheter baserade på QSE- och FMC-kontakter. (Bildkälla: Adam Taylor)

Figur 4: Utvecklingssatsen Ti180 M484 visas med sitt mångsidiga utbud av expansionsmöjligheter baserade på QSE- och FMC-kontakter. (Bildkälla: Adam Taylor)

Ti180-kortet innehåller även 256 Mbits LPDDR4 för att stödja det minne med hög prestanda som krävs i tillämpningar för bild- eller signalbehandling. Utvecklingskortet har även ett antal olika klockningsalternativ på 25, 33,33, 50 och 74,25 MHz som kan användas med enhetens PLL (phase lock loop) för att generera olika interna frekvenser.

Möjligheten att programmera om och felsöka på kortet i realtid under utveckling är kritiskt och kräver en JTAG-anslutning som är inbyggd via ett gränssnitt med USB-C. Det finns även ett icke-flyktigt minne i form av två stycken 256 Mbit NOR-flashenheter som kan användas för att demonstrera konfigurationslösningen.

Kortet drivs av en universell strömadapter på 12 V som medföljer i förpackningen. Dessutom ingår ett utbrytningskort för FMC-till-QSE tillsammans med QSE-baserade expansionskort för HDMI, Ethernet, MIPI och LVDS. För att demonstrera bildbehandlingskapaciteten i Ti180 finns även ett dubbelt tilläggskort med RPI och två stycken IMX477-kamerakort.

Programvarumiljön

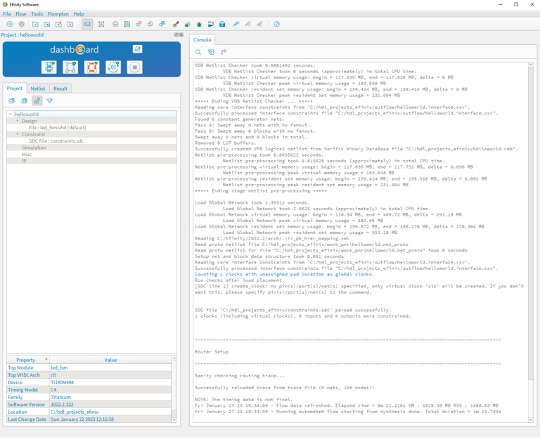

Efinix programvara Efinity används för att implementera konstruktioner som använder utvecklingskortet Ti180. Programvaran gör det möjligt att generera en bitström via syntes samt placering och routning. Den ger även utvecklare tillgång till IP-block (intellectual property), timinganalys och felsökning i kretsen.

Observera att det krävs ett utvecklingskort för att få tillgång till programvaran Efinity. Till skillnad från andra leverantörer har verktyget inte olika versioner som kräver ytterligare licenser.

I Efinity skapas nya projekt som inriktar sig på den valda enheten. RTL-filer kan sedan läggas till i projektet och begränsningar skapas för timing och I/O-konstruktion. Det är i Efinity som utvecklare även kan implementera I/O-konstruktionen genom att använda HSIO, GPIO och specialiserade I/O:ar.

Figur 5: I Efinity skapas nya projekt som riktar sig till den valda enheten. (Bildkälla: Adam Taylor)

Figur 5: I Efinity skapas nya projekt som riktar sig till den valda enheten. (Bildkälla: Adam Taylor)

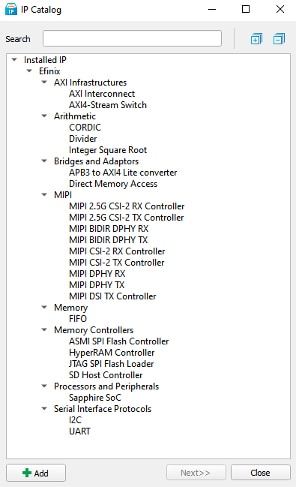

En kritisk del av FPGA-konstruktionen är nyttjandet av IP, särskilt när det gäller komplex IP som t.ex. sammankopplingar med AXI, minnesstyrningar och softcore-processorer. Efinity förser utvecklare med en rad olika IP-block som kan användas för att påskynda konstruktionsprocessen.

Figur 6: Efinity förser utvecklare med en IP-katalog som de kan använda för att påskynda konstruktionsprocessen. (Bildkälla: Adam Taylor)

Figur 6: Efinity förser utvecklare med en IP-katalog som de kan använda för att påskynda konstruktionsprocessen. (Bildkälla: Adam Taylor)

Även om FPGA:er är utmärkta för att implementera parallella bearbetningsstrukturer innehåller många FPGA-konstruktioner softcore-processorer. Dessa skapar en möjlighet att genomföra sekventiell bearbetning, som t.ex. nätverkskommunikation. För att göra det möjligt att installera softcore-processorerna i enheter från Efinix tillhandahåller Efinity konfigurationsverktyget för systemkretsen Sapphire. Sapphire gör det möjligt för utvecklare att definiera ett system med flera processorer som har både cache och cachekonsekvens över flera processorer, tillsammans med möjligheten att köra ett inbäddat Linux-operativsystem. I Sapphire kan utvecklaren välja mellan en och fyra softcore-processorer.

Softcore-processorn som implementeras är VexRiscV soft CPU som är baserad på arkitekturen med en uppsättning RISC-V-instruktioner. Processorn VexRiscV är en 32-bitars implementering som har utökningar för pipelining och erbjuder en konfigurerbar funktionsuppsättning, vilket gör den idealisk för implementering i Efinix-enheter. Valfria konfigurationer inkluderar en multiplikator, atomiska instruktioner, tillägg för flyttal samt komprimerade instruktioner. Beroende på systemkretsens konfiguration kommer prestandan att ligga mellan 0,86 och 1,05 DMIPS/MHz.

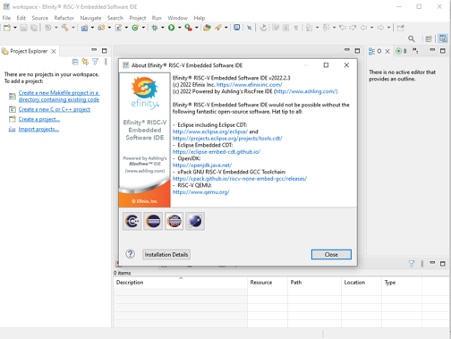

När hårdvarumiljön har konstruerats och implementerats i Efinix-enheten kan programvaran utvecklas med hjälp av Ashling RiscFree IDE. Ashling RiscFree är en IDE baserad på Eclipse som möjliggör skapande och kompilering av programvaror för tillämpning tillsammans med felsökning på målet för att finjustera tillämpningen innan införande.

Figur 7: Ashling RiscFree är en IDE baserad på Eclipse som möjliggör skapande och kompilering av programvaror för tillämpning tillsammans med felsökning på målet. (Bildkälla: Adam Taylor)

Figur 7: Ashling RiscFree är en IDE baserad på Eclipse som möjliggör skapande och kompilering av programvaror för tillämpning tillsammans med felsökning på målet. (Bildkälla: Adam Taylor)

Om en inbyggd lösning med Linux utvecklas, tillhandahålls alla nödvändiga startartefakter inklusive First Stage Boot Loader, OpenSBI, U-Boot och Linux med Buildroot. Alternativt kan utvecklaren använda FreeRTOS om en realtidslösning krävs.

Implementering av AI

Implementering av AI från Efinix bygger på användningen av RISC-V softcore. Den utnyttjar RISC-V-processorns kapacitet för anpassade instruktioner för att möjliggöra acceleration av lösningar från TensorFlow Lite. Användningen av RISC-V-processorn gör det även möjligt för användarna att skapa anpassade instruktioner som kan användas som en del av för- eller efterbehandlingen som följer efter AI-slutsatsen, vilket skapar en mer mottaglig och deterministisk lösning.

För att komma igång med en AI-implementering är det första steget att utforska ett modellzoo från Efinix, ett bibliotek med AI-/ML-modeller som optimerade för sin slutteknik. Utvecklare som arbetar med Efinix-enheter kan få tillgång till detta modellzoo och nätverket som utvecklats med hjälp av Jupyter Notebooks eller Google Colab. När nätverket har tränats kan det omvandlas från en modell med flyttal till en kvantiserad modell med hjälp av omvandlaren från TensorFlow Lite.

När det väl finns i TensorFlow Lite-formatet kan acceleratorn "tinyML" från Efinix användas för att skapa en lösning som är möjlig att driftsätta på RISC-V-lösningen. Med generatorn "tinyML" kan utvecklaren anpassa implementationen av acceleratorn och generera projektfilerna. När de används på detta sätt kan accelerationen ligga mellan 4 och 200 gånger beroende på vald arkitektur och anpassning.

Sammanfattning

Enheter från Efinix ger utvecklare flexibilitet tack vare dess unika XLR-arkitektur. Verktygskedjan ger inte bara möjlighet att implementera RTL-design utan kan även implementera komplicerade systemkretslösningar med softcore RISC-V-processorer. En AI-/ML-lösning bygger på en softcore systemkrets som gör det möjligt att använda ML-slutsatser.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.