Implementera strömsnål, kraftfull edge computing med Quantum-baserade FPGA:er från Efinix

Bidraget med av DigiKeys nordamerikanska redaktörer

2020-03-17

Konventionell molnteknik kan innebära problem med latens, datasäkerhet, användarsekretess, bandbredd och tillförlitliga anslutningar. För att undvika sådana problem försöker utvecklare och systemarkitekter övergå till s.k. edge computing. Men även edge computing innebär en rad utmaningar, rörande exempelvis kostnader, storlek, prestanda och strömförbrukning, men även skalbarhet, flexibilitet och uppgraderbarhet. Det här blir än mer uppenbart när utvecklarna förlägger allt fler funktioner och algoritmer för bildbearbetning, artificiell intelligens (AI) och maskininlärning närmare datakällan.

Utvecklarna försöker därför hitta andra lösningar än konventionella microcontrollers eller applikationsprocessorer. I stället har man börjat använda FPGA-kretsar (field-programmable gate array), som har kapacitet för parallell bearbetning. Kontinuerliga förbättringar av sådana kretsars design och implementering innebär att de uppfyller många – eller ibland samtliga – av de ovan nämnda kraven, antingen som fristående enheter eller i kombination med microcontrollers och AP:er. Men många utvecklare är inte vana vid FPGA:er och måste därför utöka sina kunskaper.

Den här artikeln handlar om att övergå från molnet till edge computing, och varför konventionella processningsarkitekturer kommer till korta när det gäller bildbearbetning, AI och maskininlärning. Vi tar också en översiktlig titt på FPGA:er och varför de ger en arkitekturmässig fördel för de dataintensiva tillämpningarna. Slutligen presenterar vi Efinixs Quantum-teknik – en ny strategi för FPGA:er – och beskriver hur denna teknik används.

Varför edge computing?

I konventionella molnsystem samlas data in från ett oändligt antal platser, för att sedan lagras i systemet och ligga till grund för analyser. Men det finns många nackdelar med den metoden, exempelvis kostnader för att överföra stora mängder rådata, svårigheter att säkerställa dataintegritet och datasäkerhet vid överföring, svarsfördröjningar, slutanvändarnas säkerhet, osäkra anslutningar till internet samt ineffektivt nyttjande av tillgänglig bandbredd.

Edge computing innebär, som namnet antyder (edge=kant, utkant), att man flyttar beräknings- och analyskapaciteten närmare internets kant, dvs. där informationen genereras, analyseras, samlas in och används. Termen edge computing är inte tillämpnings- eller enhetsspecifik. Utvecklarna kan välja att använda bearbetning endast vid kanten eller att nyttja både molnet och kanten.

Exempel på edge-tillämpningar är smarta fabriker, smarta städer, smarta hem och smarta transporter, för att nämna några få. Edge-enheter kan vara allt från stora, avancerade servrar till relativt små sensor- och aktuatorsystem i internets ”utkant”, dvs. där data genereras.

Fördelen med FPGA:er

Konventionella processorer är extremt effektiva när det gäller beslutsfattande och sekventiella uppgifter, men extremt ineffektiva när det gäller att hantera vissa databearbetningsalgoritmer, såsom algoritmer för bildbearbetning, AI och maskininlärning. Sådana uppgifter kan ofta brytas ned till parallella (i stället för sekventiella) bearbetningspipelines. Det råkar vara precis sådana uppgifter som nu migreras till kanten av internet, och även till den allra ”yttersta” kanten.

Eftersom FPGA-kretsar kan programmeras (konfigureras) för valfria kombinationer av funktioner, kan de köra bildbearbetnings-, AI- och maskininlärningsalgoritmer i parallella konfigurationer, vilket minimerar både strömförbrukningen och eventuella latensproblem. De starkt programmerbara FPGA-kretsarna har dessutom inbyggda block för digital signalbehandling (DSP), med särskilda multiplikatorer som väsentligt snabbar upp DSP-intensiva tillämpningar. Vidare är FPGA:erna utrustade med minnesblock som förenklar intern bearbetning (i kretsen), vilket går mycket snabbare än när bearbetningen förflyttas utanför kretsen.

Det finns ett antal FPGA-leverantörer, var och en med ett eget sortiment. En sådan leverantör är Efinix, som har utvecklat Quantum, en unik FPGA-arkitektur som är särskilt väl lämpad för edge computing i allmänhet och bildbearbetning i synnerhet. Baserat på Quantum har företaget också utvecklat sin Trion-serie av FPGA-kretsar (och Quantum-baserade ASIC-kretsar), för att erbjuda 4 gånger högre PPA (power, performance, area) än konventionell FPGA-teknik (figur 1). Trion-seriens FPGA- och ASIC-kretsar är kopplade till den integrerade utvecklingsmiljön Efinity.

Figur 1: Trion-seriens FPGA-kretsar, med extremt bra PPA (power, performance, area), används med fördel i många olika tillämpningar, såsom anpassad logik, accelererade beräkningar, maskininlärning, djupinlärning och bildbearbetning. IDE-miljön Efinity gör det möjligt att sömlöst övergå från en Trion-FPGA till en Quantum-ASIC, för ultrahög volymproduktion. (Bildkälla: Efinix)

Figur 1: Trion-seriens FPGA-kretsar, med extremt bra PPA (power, performance, area), används med fördel i många olika tillämpningar, såsom anpassad logik, accelererade beräkningar, maskininlärning, djupinlärning och bildbearbetning. IDE-miljön Efinity gör det möjligt att sömlöst övergå från en Trion-FPGA till en Quantum-ASIC, för ultrahög volymproduktion. (Bildkälla: Efinix)

Vad är Quantum?

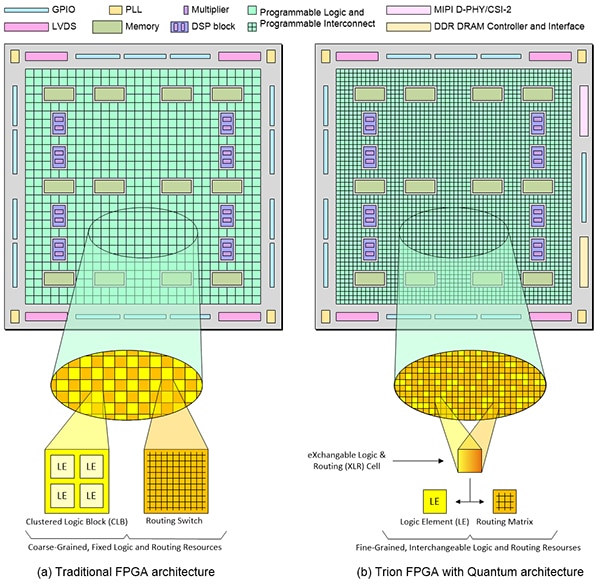

Liksom konventionella FPGA:er innehåller Trion-seriens FPGA:er minnes- och DSP-block. Skillnaden består främst i den programmerbara strukturen (figur 2). De s.k. logikelementen är hjärtat i den programmerbara logiken. Varje logikelement innehåller en uppslagtabell, en multiplexer och ett register – samtliga kan konfigureras fritt. Hos FPGA-kretsar kan den programmerbara strukturen sägas vara ”grovkornig”.

Figur 2: En konventionell FPGA-arkitektur (a) är grovkornig. Logiken och anslutningarna är programmerbara men fasta resurser. Trion-seriens FPGA-kretsar (b), som baseras på Quantum-arkitekturen, är i jämförelse finkorniga, och deras logik och routingresurser är ömsesidigt utbytbara (bildkälla: Max Maxfield)

Figur 2: En konventionell FPGA-arkitektur (a) är grovkornig. Logiken och anslutningarna är programmerbara men fasta resurser. Trion-seriens FPGA-kretsar (b), som baseras på Quantum-arkitekturen, är i jämförelse finkorniga, och deras logik och routingresurser är ömsesidigt utbytbara (bildkälla: Max Maxfield)

I grovkorniga strukturer är flera logikelement samlade i större, ”klustrade” logikblock (clustered logic block, CLB). (Alternativa benämningar på sådana logikblock är ”konfigurerbart logikblock” (configurable logic block, CLB) och logikarrayblock (logic array block, LAB), men det är samma typ av komponent.)

Notera att bilden är en abstrakt återgivning av strukturen. Logikblocken och router-switcharna (programmerbara anslutningar) i konventionella FPGA:er är inte strukturerade i rutmönster, som på bilden. Däremot är de fasta och oföränderliga på så sätt att programmeringslogiken aldrig kan bli något annat än programmeringslogik, och anslutningarna aldrig kan bli något annat än programmerbara anslutningar.

Jämfört med konventionella arkitekturer är Trion-seriens FPGA:er mycket finkornigare, ned till en upplösning på ett enda logikelement. Dessutom kan varje ”utbytbar logik- och routingcell” (exchangeable logic and routing, XLR) konfigureras att fungera som antingen ett logikelement eller som del av en routingmatris.

Konfigurationscellerna i Quantum-arkitekturen är SRAM-baserade, vilket innebär att tekniken är ”kiseloberoende”. Enheterna kan tillverkas i alla CMOS-processer av standardtyp, utan att man lägger till särskilda bearbetningssteg, vilket krävs för exempelvis flash- och antifuse-teknik, som används i vissa FPGA:er.

Det är denna konfigurerbara logik, liksom anpassningsbar routing- och anslutningskapacitet, som ger den Quantum-baserade strategin fyra gånger bättre PPA (power, performance area) än konventionella SRAM-baserade FPGA:er i samma processnod.

För FPGA:er som baseras på Quantum-arkitekturen krävs endast 7 metalliseringsskikt, i stället för minst 12 skikt, som hos konventionella FPGA:er. Varje ytterligare metallskikt innebär fler mask- och processteg. Med endast 7 skikt minskar därför design- och tillverkningskostnaderna, så att lönsamheten förbättras.

Ovanstående egenskaper och funktioner är mycket fördelaktiga om man eftersträvar kostnads-, storleks- och flexibilitetsfördelar för edge computing och bildbearbetning. Det här innebär att Trion-seriens FPGA:er är perfekt lämpade för både konventionella FPGA-tillämpningar och för moderna edge computing- och bildbearbetningstillämpningar. Exempel på edge computing- och bildbearbetningstillämpningar är mobila tillämpningar, IoT (Internet of Things), automation, robotteknik, sensorfusion, datorseende, AI och maskininlärning.

Strukturen hos Trion-seriens FPGA:er

Trion-seriens FPGA:er tillverkas i en 40 nm energieffektiv kiselprocess med mellan 4 000 och 200 000 logikelement, men processen kan anpassas för mycket större enheter. Samtliga FPGA:er i Trion-serien innehåller minnes- och DSP-block, men deras kapacitet och antal beror på enhetens storlek. Mindre enheter, som T4F81C2, är mer slimmade (med t.ex. 3 888 logikenheter, 78 848 minnesbitar och 59 GPIO-stift) och främst avsedda för handhållna enheter och funktioner i kontrollagret.

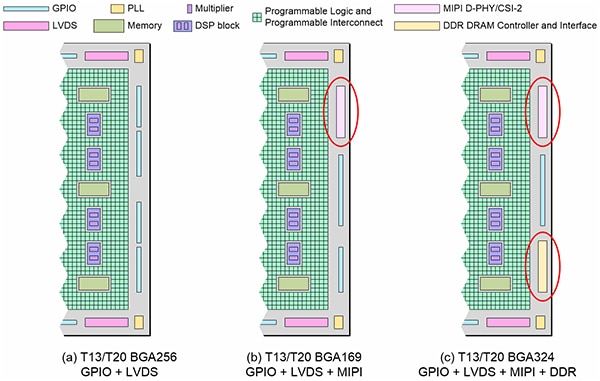

Mer avancerade enheter, som T20F256C3, har större resurser (t.ex. 19 728 logikenheter, 1 069 548 minnesbitar och 195 GPIO-stift). T13F256C3 liknar T20F256C3, men har 12 828 logikenheter. Enheter som T13/T20 finns dessutom i olika versioner (figur 3).

Figur 3: T13/T20 BGA256s (a) från Efinix är generiska FPGA-kretsar och ett bra val för I/O-intensiva system. T13/T20 BGA169s (b) har två fasta block för MIPI D-PHY/MIPI CSI-2, för system som måste ha stöd för kameragränssnittet MIPI. T13/T20 BGA324s (c) utökar MIPI-gränssnitten med ett fast x16-bitars DDR-DRAM-gränssnitt och styrenhet för bandbreddskrävande system. (Bildkälla: Max Maxfield)

Figur 3: T13/T20 BGA256s (a) från Efinix är generiska FPGA-kretsar och ett bra val för I/O-intensiva system. T13/T20 BGA169s (b) har två fasta block för MIPI D-PHY/MIPI CSI-2, för system som måste ha stöd för kameragränssnittet MIPI. T13/T20 BGA324s (c) utökar MIPI-gränssnitten med ett fast x16-bitars DDR-DRAM-gränssnitt och styrenhet för bandbreddskrävande system. (Bildkälla: Max Maxfield)

MIPI CSI-2 är det vanligaste kameragränssnittet för mobila enheter och annan teknik, tack vare låg energiförbrukning, låg latens och låg kostnad för anslutning mellan kretsar. Gränssnittet har också stöd för en rad videoformat, inklusive 1080p, 4K, 8K (och högre) samt högupplösta bilder. Särskilt intressant här är att MIPI CSI-2 är det dominerande gränssnittet för kamerasensorer i edge-tillämpningar. För att ge stöd för sådana tillämpningar har FPGA-kretsarna T13/T20 BGA169s två fasta block för MIPI D-PHY/CSI-2 (figur 3).

DDR-minne ger stöd för stora bandbredder, men kräver ett strikt timingprotokoll. Utöver de fasta MIPI-gränssnitten D-PHY/CSI-2 har T13/T20 BGA324s (figur 3, ytterligare en gång) ett fast x16-bitars DDR-DRAM-gränssnitt och styrning, för bandbreddskrävande system.

Quantum-baserade ASIC-kretsar

Som har beskrivits ovan, är konfigurationscellerna i Trion-seriens FPGA:er SRAM-baserade. Det innebär att kretsarna ifråga, när systemet startas, måste läsa in sina konfigurationsdata, antingen från en extern minnesenhet eller med hjälp av programvara (”bit-banging”) via värdprocessorn. För att möjliggöra detta vid produktion av stora volymer, erbjuder Efinix även ”Quantum Accelerated embedded” FPGA-lösningar (eFPGA) i form av Quantum-baserade ASIC-kretsar. Det innebär att Efinix kan ta T4-, T8-, T13- eller T20-system och skapa maskprogrammerade Quantum-baserade ASIC-versioner som startar internt, utan att det krävs en extern konfigurationsenhet.

Design och utveckling med Trion-seriens FPGA:er

Efinix har ett brett sortiment av utvärderingskort och utvecklarpaket som hjälper användarna att bekanta sig med Trion-produkterna. Exempel är Trion T8F81C-DK T8 Trion FPGA utvecklarpaket, Trion T20F256C-DK T20 Trion FPGA utvärderingskort och Trion T20MIPI-DK T20 MIPI D-PHY/CSI-2 utvecklarpaket.

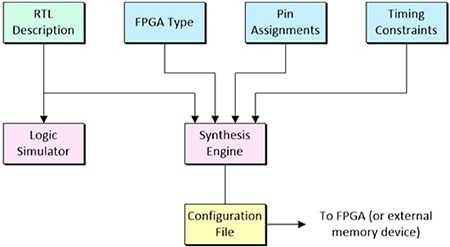

En av de vanligaste teknikerna som används vid utveckling med FPGA:er är språkbaserad design (LDD). Detta innefattar att åskådliggöra ”designavsikten” på en abstraktionsnivå känd som RTL (Register Transfer Level), med hjälp av maskinvarubeskrivande språk (HDL), till exempel Verilog eller VHDL. Efter verifiering via logisk simulering matas denna representation in i en syntesmotor, tillsammans med ytterligare information, som typ av mål-FPGA, stifttilldelning och tidsbegränsningar (till exempel fördröjning mellan ingång och utgång). Utmatningen från syntesmotorn är en konfigurationsfil, vilken antingen hämtas direkt till FPGA:n eller till ett externt minne (figur 4).

Figur 4: Efter verifiering via logisk simulering matas designbeskrivningen för RTL in i en syntesmotor, tillsammans med ytterligare designdetaljer, som FPGA-typ, stifttilldelning och tidsbegränsningar. Utmatningen från syntesmotorn är en konfigurationsfil, vilken hämtas direkt till FPGA:n. (Bildkälla: Max Maxfield)

Figur 4: Efter verifiering via logisk simulering matas designbeskrivningen för RTL in i en syntesmotor, tillsammans med ytterligare designdetaljer, som FPGA-typ, stifttilldelning och tidsbegränsningar. Utmatningen från syntesmotorn är en konfigurationsfil, vilken hämtas direkt till FPGA:n. (Bildkälla: Max Maxfield)

Efinity IDE från Efinix tillhör den här klassen av verktyg. Programvaran ger ett fullständigt flöde från RTL till bitström, med ett enkelt och användarvänligt GUI (grafiskt användargränssnitt) och stöd för kommandoradsskript. En intuitiv instrumentpanel vägleder utvecklaren genom flödet (dvs. syntes, placering, routing, generering av bitström), där varje fas kan styras automatiskt eller manuellt. Utvecklarna kan använda Efinitys syntesmotor för att nyttja alla fördelar med Quantum-arkitekturen i Trion-seriens FPGA:er och generera enheter med 4 gånger bättre PPA.

Efinity IDE stöder simuleringsflöden med ModelSim, NCSim eller kostnadsfria IVerilog-simulatorer, men har även en ”Interface Designer” för att anpassa logik och tilldela stift till block i enhetsperiferin. Vidare finns en ”Floorplan Editor” för att gå igenom systemets logik och placering; en ”Timing Browser” och statisk timinganalys för att mäta systemets prestanda; en integrerad hårdvarufelsökare med kärnor för logikanalys och virtuell I/O-felsökning.

Slutsatser

När utvecklarna väljer att förlägga allt fler bildbearbetnings-, AI- och maskininlärningsuppgifter i kanten av internet – antingen som komplement till molnet eller som alternativ till det – bör de överväga att använda FPGA-kretsar som del av arkitekturen, för att hantera eventuella problem med kostnader, prestanda, strömförbrukning, storlek, skalbarhet, flexibilitet och uppgraderbarhet.

Det här kan innebära att enskilda utvecklare måste utöka sina kunskaper, men som framgår av den här artikeln kan utvecklingen inom FPGA-teknik, exempelvis i form av Quantum från Efinix, göra att satsningen lönar sig tack vare lägre kostnader, mindre format, högre prestanda och högre flexibilitet.

Numera finns FPGA:er som lämpar sig för både konventionella FPGA-tillämpningar och för edge computing med koppling till mobila enheter, IoT, automation, robotsystem, sensorfusion, datorseende, AI och maskininlärning.

Ytterligare resurser

- Grundprinciper: IoT, IIoT, AIoT och varför de är framtiden inom industriautomation

- Grundprinciper för FPGA:er: Vad är FPGA:er och varför behövs de?

- Grundprinciper för FPGA – del 2: Komma igång med FPGA:er från Lattice Semiconductor

- Grundprinciper för FPGA – del 3: Komma igång med FPGA:er från Microchip Technology

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.