Grundprinciper för FPGA:er: Vad är FPGA:er och varför behövs de?

Bidraget med av DigiKeys nordamerikanska redaktörer

2019-11-14

Optimala processningslösningar hittas ofta genom kombinationer av RISC, CISC, grafikprocessorer och FPGA:er, FPGA:er på egen hand eller genom FPGA:er som har hårda processorkärnor som en del av sin struktur. Dock är många konstruktörer inte bekanta med FPGA:ers funktioner, hur de har utvecklats och hur de används. I denna artikel, del 1 i en serie av fem, pratar vi om grundläggande om FPGA:er och presenterar exempellösningar från större leverantörer. Del 2, del 3, del 4 och del 5 kommer att fokusera på FPGA-produktfamiljer och konstruktionsverktyg från Lattice Semiconductor, Microchip, Altera och Xilinx.

Konstruktörer letar ständigt efter sätt att utforma sina system för att kunna erbjuda en optimal processningslösning som uppfyller alla deras tillämpningskrav. I många situationer kräver den optimala lösningen ofta att man använder fältprogrammerbara gatematriser (FPGA:er), men många konstruktörer är tyvärr förvånansvärt obekanta med dessa enheters funktion, samt hur de kan integreras.

Den här artikeln beskriver kort olika konstruktionsscenarier där man kan dra nytta av FPGA:er. Därefter beskrivs grundprinciperna för hur de fungerar innan några intressanta FPGA-lösningar och utvecklingssatser introduceras.

Varför använda FPGA-kretsar?

Det finns ett stort urval beräkningstillämpningar som var och en kan gynnas av olika metoder, inklusive färdiga mikroprocessorer (MPU:er) och microcontrollers (MCU:er), färdiga grafikprocessorer (GPU:er), FPGA:er och skräddarsydda SoC-enheter (system-on-chip). Att avgöra vilken som passar bäst kräver en närmare titt på tillämpningens unika krav och förutsättningar.

Till exempel: vid arbete med den senaste tekniken som 5G-basstationer, måste konstruktörerna tänka på att underliggande standarder och protokoll fortfarande utvecklas. Detta innebär att konstruktörerna måste kunna reagera snabbt och effektivt på eventuella förändringar i specifikationer som ligger utanför deras kontroll.

De behöver även vara flexibla och kunna reagera på framtida förändringar av standarder och protokoll som sker efter att systemen har tagits i drift i fält. Det är även nödvändigt att kunna svara på oväntade fel i systemfunktioner eller brister i systemsäkerheten, att modifiera befintliga funktioner eller lägga till nya funktioner för att förlänga systemets livslängd.

En SoC ger normalt högst prestanda, men det är ett dyrt och tidskrävande alternativ. Dessutom så är algoritmer som implementeras i kretsens struktur i princip "låsta i kisel". Den här inbyggda oflexibiliteten blir ett problem med tanke på omständigheterna ovan. För att hitta den perfekta punkten med optimal prestanda och flexibilitet krävs en alternativ väg. Den bygger oftast på FPGA:er, kombinationer av mikroprocessorer/microcontrollers och FPGA:er eller FPGA:er med interna processorkärnor.

Vad är FPGA:er?

Det är en svår fråga eftersom FPGA:er är många olika saker för olika personer. Det finns dessutom många typer av FPGA:er som alla har olika kombinationer av egenskaper och funktioner.

I hjärtat av en FPGA – den definierande egenskapen för FPGA:er kan man säga – finns den programmerbara strukturen, som presenteras som en matris av programmerbara logikblock (figur 1a). Vart och ett av dessa logiska block innehåller en samling element – inklusive en uppslagstabell (LUT), en multiplexer och ett register – varav alla kan konfigureras (programmeras) för att fungera som tänkt (figur 2).

Figur 1: De enklaste FPGA:erna innehåller endast programmerbar struktur och konfigurerbara GPIO:er (a), olika arkitekturer förstärker den grundläggande strukturen med SRAM-block, PLL:er och klockhanterare (b), DSP-block och SERDES-gränssnitt (c) samt interna processorkärnor och kringutrustning (d). (Bildkälla: Max Maxfield)

Figur 1: De enklaste FPGA:erna innehåller endast programmerbar struktur och konfigurerbara GPIO:er (a), olika arkitekturer förstärker den grundläggande strukturen med SRAM-block, PLL:er och klockhanterare (b), DSP-block och SERDES-gränssnitt (c) samt interna processorkärnor och kringutrustning (d). (Bildkälla: Max Maxfield)

Figur 2: Vart och ett av dessa logiska block innehåller en samling element, inklusive en uppslagstabell, en multiplexer och ett register, varav alla kan konfigureras (programmeras) för att fungera som tänkt. (Bildkälla: Max Maxfield)

Figur 2: Vart och ett av dessa logiska block innehåller en samling element, inklusive en uppslagstabell, en multiplexer och ett register, varav alla kan konfigureras (programmeras) för att fungera som tänkt. (Bildkälla: Max Maxfield)

Många FPGA:er använder LUT:er med 4 ingångar som kan konfigureras för att implementera valfria logikfunktioner med 4 ingångar. För att bättre kunna stödja de breda databanor som används i vissa tillämpningar erbjuder vissa FPGA:er LUT:er med 6, 7 eller till och med 8 ingångar. Utgången från LUT är direkt ansluten till en av de logiska blockutgångarna och till en av multiplexeringångarna. Den andra ingången till multiplexern är direkt ansluten till en logikblockingång (e). Multiplexern kan konfigureras för att välja någon av dessa ingångar.

Utgången från multiplexern matar registeringången. Varje register kan konfigureras för att användas som en flanktriggad vippa eller en nivåkänslig låskrets (dock rekommenderas inte asynkron logik i form av låskretsar inuti FPGA:erna). Varje registers klocka (eller enable-signal) kan konfigureras för att vara aktiv hög eller aktiv låg. På liknande sätt kan den aktiva nivån för de inställda/återställda ingångarna också konfigureras.

Dessa logikblock kan ses som "öar av programmerbar logik" som flyter i ett "hav av programmerbara anslutningar". Sammankopplingen kan konfigureras för att ansluta valfri utgång från ett logikblock till valfri ingång på de andra logikblocken. De primära ingångarna på FPGA kan dessutom anslutas till ingångarna på logikblock, och utgångarna från eventuella logikblock kan användas för att driva de primära utgångarna från enheten.

När det gäller de huvudsakliga universella ingångarna/utgångarna (GPIO:er), presenteras de i grupper, där varje grupp kan konfigureras för att stödja en annan gränssnittsstandard som LVCMOS, LVDS, LVTTL, HSTL eller SSTL. Dessutom kan ingångarnas impedans konfigureras liksom utgångarnas ändringshastighet.

Nästa steg i FPGA-strukturen innehåller bl.a. SRAM-block, som kallas block-RAM (BRAM), faslåsta slingor (PLL:er) och klockhanterare (figur 1b). Digitala signalbehandlingsblock (DSP-lager) kan också läggas till. De innehåller konfigurerbara multiplicerare och en konfigurerbar adderare som tillåter dem att utföra MAC-åtgärder (multiply-accumulate) (figur 1c).

En annan vanlig FPGA-funktion, höghastighets-SERDES-block, kan ge stöd för gigabit-seriegränssnitt. Det är viktigt att notera att FPGA:er ger stöd för alla ovannämnda funktioner. Olika FPGA:er erbjuder olika samlingar av funktioner som riktar sig till olika marknader och tillämpningar.

Den programmerbara strukturen i en FPGA kan användas för att implementera logiska funktioner eller en samling av funktioner, hela vägen upp till en processorkärna eller till och med flera kärnor. Om dessa kärnor implementeras i en programmerbar struktur kallas de "mjukvarukärnor". Som en jämförelse innehåller vissa FPGA:er som oftast kallas SoC FPGA:er en eller flera "maskinvaruprocessorer" som implementeras direkt i kiselmaterialet (figur 1d). Dessa maskinvaruliknande processorkärnor kan inkludera flytpunktsenheter (FPU:er) och L1/L2-cache.

På liknande sätt kan perifera gränssnittsfunktioner som CAN, I2C, SPI, UART och USB implementeras som mjukvarukärnor i den programmerbara strukturen, men många FPGA:er inkluderar dem som maskinvarukärnor i kiselmaterialet. Kommunikation mellan processorkärnorna, gränssnittsfunktionerna och programmerbar struktur sker oftast med höghastighetsbussar som AMBA och AXI.

De första FPGA:erna, som presenterades på marknaden av Xilinx 1985, innehöll endast en 8 x 8-matris med programmerbara logikblock (inga RAM-block, DSP-block osv.). Som en jämförelse kan dagens avancerade FPGA:er innehålla hundratusentals logikblock, tusentals DSP-block och flera megabit RAM. Sammanlagt kan de innehålla miljarder transistorer, vilket motsvarar tiotals miljoner motsvarande grindar (t.ex. NAND-grindar med två ingångar).

Alternativa konfigurationstekniker

Sättet som logikblocken fungerar på och som dragningen av hopkopplingen avgörs på, sker genom konfigurationsceller, som kan visualiseras som 0/1-strömställare (av/på). Dessa celler används även för att konfigurera GPIO:ernas gränssnittsstandard, ingångsimpedans, utgående ändringshastighet osv. Beroende på FPGA:n kan dessa konfigurationsceller implementeras med en av tre tekniker:

- Antifuse: Dessa konfigurationsceller kan programmeras en gång (OTP), vilket innebär att när enheten har programmerats är det oåterkalleligt. Dessa enheter brukar begränsas till rymdindustri- och högsäkerhetstillämpningar. Eftersom de säljs i små kvantiteter är de dyra designalternativ.

- Flash: Som antifuse-baserade konfigurationsceller är flashbaserade celler icke-flyktiga. Till skillnad från antifuse-celler kan flash-celler omprogrammeras efter behov. Flashkonfigurationsceller är motståndskraftiga mot strålning, vilket gör dem lämpliga för rymdtillämpningar (dock med modifieringar i deras övre metalliseringslager och höljen).

- SRAM: I det här fallet lagras konfigurationsdata i ett externt minne från vilket den läses in varje gång FPGA aktiveras (eller enligt anvisningarna vid dynamiska konfigurationsscenarier).

Fördelen med FPGA:er med antifuse- eller flash-baserade konfigurationsceller är att de alltid är på och har låg effektförbrukning. En nackdel med dessa tekniker är att de kräver ytterligare bearbetningssteg utöver den underliggande CMOS-processen som används för att skapa resten av kretsen.

Fördelen med FPGA:er vars konfigurationsceller baseras på SRAM-teknik är att de tillverkas med samma CMOS-process som resten av kretsen och ger högre prestanda eftersom de normalt sett ligger en eller två generationer före antifuse- och flash-tekniken. Huvudnackdelarna är att SRAM-konfigurationsceller förbrukar mer effekt än motsvarande antifuse- och flash-komponenter (i samma tekniknod) och att de är känsliga för SEU-händelser (single event upsets) som orsakas av strålning.

Under en lång tid innebar detta att SRAM-baserade FPGA:er ansågs olämpliga i flyg- och rymdtillämpningar. På senare tid har särskilda tillnärmningsstrategier tillämpats, vilket innebär att SRAM-baserade FPGA:er nu återfinns i system som Mars Curiosity Rover, tillsammans med flash-baserade varianter.

Att använda FPGA:er ger flexibilitet

FPGA:er används för många olika tillämpningar. De är särskilt lämpliga för att implementera smarta gränssnittsfunktioner, motorreglering, algoritmacceleration och högkapacitetsberäkningar (HPC), bild- och videobehandling, maskinsyn, artificiell intelligens (AI), maskininlärning (ML), djupinlärning (DL), radar, strålformning, basstationer och kommunikation.

Ett enkelt exempel är att tillhandahålla ett smart gränssnitt mellan andra enheter som använder olika gränssnittsstandarder eller kommunikationsprotokoll. Tänk på ett befintligt system som innehåller en applikationsprocessor som är ansluten till en kamerasensor och en displayenhet med föråldrade gränssnitt (figur 3a).

Figur 3: En FPGA kan användas för att tillhandahålla ett smart gränssnitt mellan andra enheter som använder olika gränssnittsstandarder eller kommunikationsprotokoll och därigenom utökar livslängden hos befintliga konstruktioner som baseras på föråldrade enheter. (Bildkälla: Max Maxfield)

Figur 3: En FPGA kan användas för att tillhandahålla ett smart gränssnitt mellan andra enheter som använder olika gränssnittsstandarder eller kommunikationsprotokoll och därigenom utökar livslängden hos befintliga konstruktioner som baseras på föråldrade enheter. (Bildkälla: Max Maxfield)

Anta nu att systemkonstruktörerna vill uppgradera kamerasensorn och displayenheten till något modernare som är lättare, billigare och förbrukar mindre effekt. Det enda problemet är att en eller båda av dessa kringenheter kan använda en modern gränssnittsstandard som inte stöds av den ursprungliga applikationsprocessorn (AP). De kan även har stöd för ett helt annat kommunikationsprotokoll som MIPI (Mobile Industry Processor Interface). I det här fallet ger en FPGA med sin förmåga att stödja flera I/O-standarder, i kombination med några programvaru-MIPI IP-kärnor en snabb, billig, riskfri uppgraderingsväg (figur 3b).

Som ett annat tillämpningsexempel kan vi tänka oss en beräkningsintensiv uppgift som att utföra signalbehandlingen som krävs för att implementera ett radarsystem eller strålformningen i en kommunikationsbasstation. Vanliga processorer med sina Neumann- eller Harvard-arkitekturer är väl anpassade för vissa uppgifter, men de är mindre lämpliga för uppgifter som kräver att samma åtgärdssekvens ska utföras upprepade gånger. Detta beror på att en enda processor som kör en enda tråd endast kan köra en instruktion åt gången (figur 4a).

Figur 4: Till skillnad från mikroprocessorer där endast en enda instruktion kan köras åt gången (sekventiellt) kan flera funktionsblock i en FPGA köras samtidigt. Dessutom kan FPGA:er implementera lämpliga algoritmer parallellt i hög grad. (Bildkälla: Max Maxfield)

Figur 4: Till skillnad från mikroprocessorer där endast en enda instruktion kan köras åt gången (sekventiellt) kan flera funktionsblock i en FPGA köras samtidigt. Dessutom kan FPGA:er implementera lämpliga algoritmer parallellt i hög grad. (Bildkälla: Max Maxfield)

Som jämförelse kan flera funktioner köras samtidigt i en FPGA och därigenom kan en serie åtgärder läggas i kö, vilket i sin tur möjliggör mycket högre genomströmning. Istället för att utföra samma åtgärd ytterligare t.ex. 1 000 gånger på 1 000 dataparvärden med processorn, kan samma beräkningar utföras parallellt i en enda klockcykel i FPGA genom att instantiera 1 000 adderare i den programmerbara strukturen (figur 4b).

Vem tillverkar FPGA:er?

Det är ett landskap under ständig utveckling. De två huvudtillverkarna av verkligt kraftfulla enheter med högsta kapacitet och prestanda är Intel (som förvärvat Altera) och Xilinx.

Intels och Xilinx utbud sträcker sig från enklare FPGA:er till avancerade SoC FPGA:er. En annan leverantör som fokuserar nästan enbart på FPGA:er är Lattice Semiconductor, som riktar in sig på tillämpningar på låg- och mellannivå. Sist men inte minst har Microchip Technology (via sina förvärv av Actel, Atmel och Microsemi) nu ett team med flera familjer av små till medelstora FPGA:er, samt en del produkter i de lägre skikten av kategorin SoC FPGA.

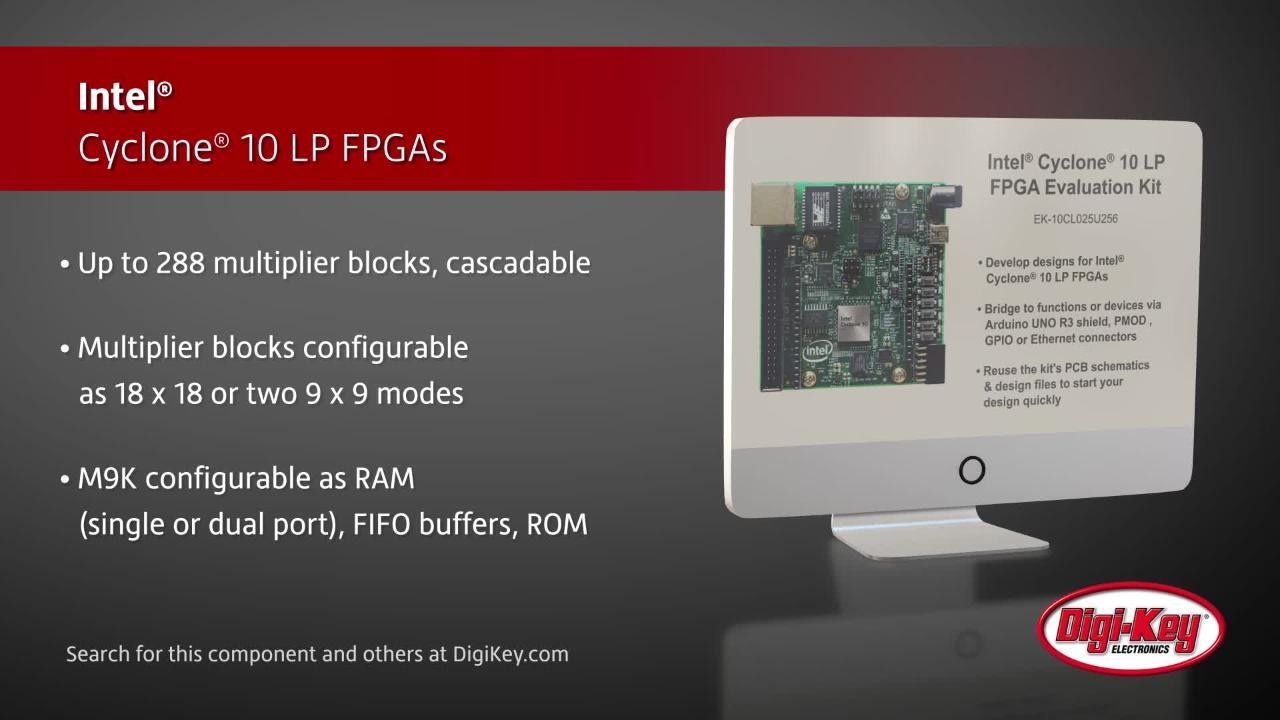

Det kan vara svårt att välja den bästa enheten för en uppgift eftersom det finns så många familjer som var och en erbjuder olika resurser, prestanda, kapaciteter och kapslingstyper. Här är några exempel på enheter från Intel, Lattice Semiconductor och Xilinx.

Hur konstruerar man med FPGA:er?

Det traditionella sättet att konstruera FPGA:er är att konstruktörerna använder ett maskinvaruspråk som Verilog eller VHDL för att fånga konstruktionens avsikt. Dessa beskrivningar kan först simuleras för att kontrollera att de presterar som avsett och sedan förmedlas till ett syntesverktyg som genererar konfigurationsfilen som används för att konfigurera (programmera) FPGA:n.

Varje FPGA-återförsäljare har antingen en internutvecklad verktygskedja eller erbjuder en anpassad version av ett verktyg från en specialiserad återförsäljare. I båda fallen ges tillgång till verktygen via FPGA-återförsäljarens webbplats, men det kan även finnas kostnadsfria eller billiga versioner av de fullständiga verktygssviterna.

För att göra FPGA:erna mer tillgängliga för programvaruutvecklare erbjuder vissa FPGA-återförsäljare nu HLS-verktyg (high-level synthesis). Dessa verktyg tolkar en algoritmbeskrivning av det önskade beteendet på en hög abstraktionsnivå i C, C++ eller OpenCL och genererar insignalerna för att mata syntesmotorn på lägre nivå.

För konstruktörer som vill komma igång finns många utvecklings- och utvärderingskort som alla erbjuder olika funktioner och egenskaper. Tre exempel är utvecklingssatsen DFR0600 från DFRobot som har en Zynq-7000 SoC FPGA från Xilinx, DE10 Nano från Terasic Inc. med en Cyclone V SoC FPGA från Intel och utvärderingskortet ICE40HX1K-STICK-EVN som har en iCE40 FPGA med låg effekt från Lattice Semiconductor.

Konstruktörer som planerar att använda ett FPGA-baserat PCIe-dotterkort för att accelerera tillämpningar som körs på ett X86-moderkort kan fundera på något av Alveo PCIe-dotterkorten, som också kommer från Xilinx.

Slutsatser

Optimala konstruktionslösningar hittas ofta i form av FPGA:er, kombinationer av processorer och FPGA:er eller genom FPGA:er med hårda processorkärnor inbyggda i strukturen.

FPGA:erna har utvecklats snabbt under åren och uppfyller många konstruktionskrav när det gäller flexibilitet, databehandlingshastighet och prestanda, vilket gör dem användbara i många olika tillämpningar.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.