Grundprinciper för FPGA:er – del 4: Komma igång med FPGA:er från Xilinx

Bidraget med av DigiKeys nordamerikanska redaktörer

2020-04-01

Redaktörens anmärkning: optimala processningslösningar skapas ofta genom kombinationer av RISC, CISC, grafikprocessorer och FPGA:er, genom FPGA:er på egen hand eller genom FPGA:er med interna processorkärnor. Dock är många konstruktörer obekanta med FPGA:ernas funktioner, hur de har utvecklats och hur de används. Del 1 i denna serie innehåller en inledning på hög nivå till FPGA:er. I del 2 gick vi in på FPGA:er från Lattice Semiconductor. I del 3 tittade vi närmare på FPGA-familjer och konstruktionsverktyg från Microchip Technology (via deras dotterbolag Microsemi Corporation). Här i del 4 ska vi se lite närmare på komponenter och verktyg från Xilinx. I del 5 kommer vi att se vilka produkter Altera har att erbjuda.

Elektriskt programmerbara grindmatriser (FPGA:er) har – som vi diskuterade i del 1 – många egenskaper som gör dem till en ovärderlig tillgång vid databeräkningar (antingen använda fristående eller i en heterogen arkitektur) men många konstruktörer är fortfarande inte bekanta med FPGA:er och hur dessa enheter kan användas i deras konstruktioner.

Ett sätt att åtgärda detta är att titta närmare på FPGA-arkitekturer och relaterade verktyg från större leverantörer, och i den här artikeln har vi valt att titta lite närmare på produkter från Xilinx.

Översikt över alternativ inom högnivå-FPGA:er

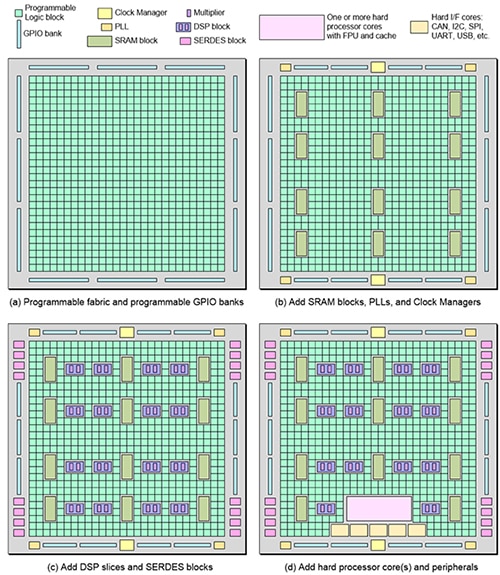

Det finns många typer av FPGA:er på marknaden, alla med olika kombinationer av egenskaper och funktioner. Hjärtat i FPGA:er är den programmerbara strukturen. Denna presenteras som en matris med programmerbara logikblock, vilka även kallas logikelement (LE) (figur 1a). Nästa steg i FPGA-strukturen innehåller bland annat SRAM-block, som kallas block-RAM (BRAM), faslåsta slingor (PLL:er) och klockhanterare (figur 1b). Digitala signalbehandlingsblock (signalprocessor) och snabba SERDES-block (serialisatorer/deserialisatorer) kan också läggas till (figur 1c).

Figur 1: De enklaste FPGA:erna innehåller endast programmerbar struktur och konfigurerbara GPIO:er (General-Purpose IO) (a); olika arkitekturer förstärker den grundläggande strukturen med SRAM-block, PLL:er och klockhanterare (b); signalprocessorblock och SERDES-gränssnitt (c); samt interna processorkärnor och kringutrustning (d). (Bildkälla: Max Maxfield)

Figur 1: De enklaste FPGA:erna innehåller endast programmerbar struktur och konfigurerbara GPIO:er (General-Purpose IO) (a); olika arkitekturer förstärker den grundläggande strukturen med SRAM-block, PLL:er och klockhanterare (b); signalprocessorblock och SERDES-gränssnitt (c); samt interna processorkärnor och kringutrustning (d). (Bildkälla: Max Maxfield)

Perifera gränssnittsfunktioner som CAN, I2C, SPI, UART och USB kan implementeras som mjukvarukärnor i den programmerbara strukturen, men många FPGA:er inkluderar dem som maskinvarukärnor i kiselmaterialet. På samma sätt kan mikroprocessorer implementeras som mjukvarukärnor i den programmerbara strukturen eller som hårdvarukärnor i kiselmaterialet (figur 1d). FPGA:er med interna processorkärnor kallas SoC-FPGA:er (system-on-chip). Olika FPGA:er erbjuder olika uppsättningar funktioner, egenskaper och kapaciteter som riktar sig till olika marknader och tillämpningar.

Det finns flera olika FPGA-leverantörer, inklusive Altera (nu uppköpta av Intel), Atmel (uppköpta av Microchip Technology), Efinix, Lattice Semiconductor, Microsemi (också uppköpta av Microchip Technology) och Xilinx.

Alla dessa leverantörer erbjuder flera olika modeller av FPGA:er – vissa erbjuder SoC-FPGA:er, andra erbjuder enheter avsedda för tillämpningar inom AI och maskininlärning och vissa erbjuder strålningståliga enheter för omgivningar med höga strålningsnivåer (vid exempelvis användning i rymden). Det kan vara svårt att välja den bästa enheten för en uppgift eftersom det finns så många olika familjer som var och en erbjuder olika resurser.

Introduktion till Xilinx FPGA, SoC, MPSoC, RFSoC och ACAP

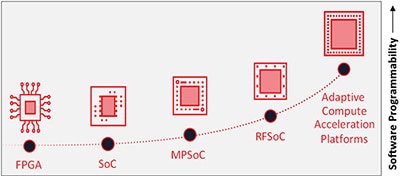

Prestanda och egenskaper för de programmerbara enheterna från Xilinx finns i alla nivåer, från enkla till mycket avancerade enheter. Från traditionella FPGA:er till SoC (FPGA-programmerbar struktur med en hård processorkärna), MPSoCr (FPGA-programmerbar struktur med flera hårda processorkärnor), RFSoC (MPSoC:er med RF-kapacitet) och ACAP (Adaptive Compute Acceleration Platforms) (figur 2).

Figur 2: Xilinx arkitekturprodukter har över tid utvecklats från att vara enkla FPGA:er med endast programmerbar struktur till att bli SoC-enheter i vilka den programmerbara strukturen utökas med en hård processorkärna. Därifrån har de utvecklats vidare till MPSoC:er med flera processorer, RFSoC:er med RF-kapacitet och nu den senaste generationen ACAP:er som är avsedda för tillämpningar som AI. (Bildkälla: Max Maxfield)

Figur 2: Xilinx arkitekturprodukter har över tid utvecklats från att vara enkla FPGA:er med endast programmerbar struktur till att bli SoC-enheter i vilka den programmerbara strukturen utökas med en hård processorkärna. Därifrån har de utvecklats vidare till MPSoC:er med flera processorer, RFSoC:er med RF-kapacitet och nu den senaste generationen ACAP:er som är avsedda för tillämpningar som AI. (Bildkälla: Max Maxfield)

För den som är ny inom FPGA:er kan det vara svårt att få en övergripande bild över Xilinx omfattande produktsortiment, som spänner över många olika marknadssegment och distributionsmetoder.

Bland de marknader där Xilinx finns kan nämnas datacenter (databeräkning, nätverk, lagring), kommunikation (fast, trådlös), flyg- och försvarssektorn, industri, forskning och medicin (ISM), test, mätning och emulering (TME) samt fordonsindustri, media och konsumentprodukter.

Bland distributionsmetoderna finns det som Xilinx kallar Hardware Adaptable Devices (vilket omfattar chip, utvärderingskort och utvecklarpaket), Deployable End-Systems, vilket omfattar SOM-moduler (system-on-modules) och PCIe-acceleratorkort samt FAAS (FPGA-as-a-service), vilket omfattar utvärdering och användning av Xilinx teknologi via ledande molnleverantörer som Amazon Web Services (AWS), Alibaba.com och Nimbix.net

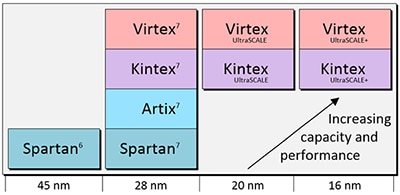

Ett sätt att kategorisera Xilinx FPGA-produkter är efter deras processnoder (figur 3).

Figur 3: Xilinx FPGA-produkter ger ett omfattande utbud med produkter med flera noder för många olika tillämpningar. (Bildkälla: Max Maxfield)

Figur 3: Xilinx FPGA-produkter ger ett omfattande utbud med produkter med flera noder för många olika tillämpningar. (Bildkälla: Max Maxfield)

Beroende på vilken tillämpning det handlar om, kan konstruktörer antingen satsa på en billig FPGA i litet fysiskt format som implementeras i en nod med tidigare teknik eller för en modern nätverksapplikation välja exempelvis en enhet med hög kapacitet, stor bandbredd och hög prestanda som implementeras i en nod med modernare teknik.

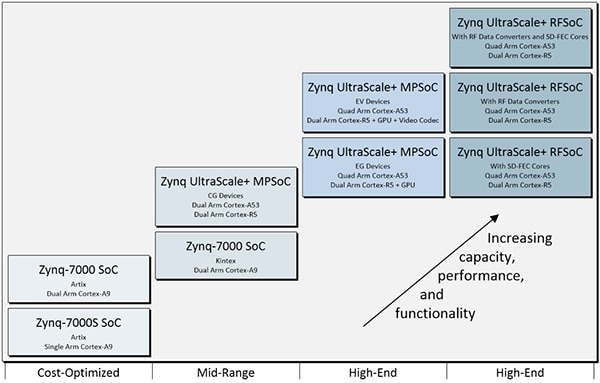

Xilinx har en serie enheter som heter Zynq och som är lämplig för konstruktioner som kräver en eller flera interna processorkärnor (och andra förstärkta funktioner som grafikprocessorer, codecar och SD-FEC-kärnor (soft decision forward error correction)). En sammanfattning av Zynq SoC, MPSoC och RFSoC visas i figur 4. Med denna svit med lösningar får konstruktörer tillgång till många olika funktioner som kan underlätta optimering av effekt, prestanda, kostnad och tid till marknad.

Figur 4: Xilinx SoC, MPSoC och RFSoC som integrerar mjukvaruprogrammerbarheten hos en processor med hårdvaruprogrammerbarheten hos en FPGA, vilket ger konstruktörer systemprestanda, flexibilitet och skalbarhet. (Bildkälla: Max Maxfield)

Figur 4: Xilinx SoC, MPSoC och RFSoC som integrerar mjukvaruprogrammerbarheten hos en processor med hårdvaruprogrammerbarheten hos en FPGA, vilket ger konstruktörer systemprestanda, flexibilitet och skalbarhet. (Bildkälla: Max Maxfield)

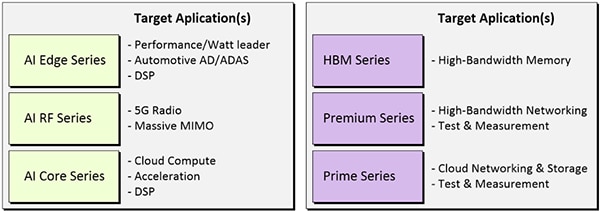

Det senaste erbjudandet från Xilinx är Versal ACAP-enheter (Adaptive Compute Acceleration Platform), vilka alla är implementerade i noder med 7 nm-processteknik. ACAP är mycket integrerade, flerkärniga plattformar som kan anpassa sig till olika och ständigt föränderliga algoritmer. De är dynamiskt anpassningsbara vad gäller både hårdvara och mjuvara, vilket gör att de passar för många olika applikationer och arbetslaster. ACAP är uppbyggda kring programmerbara NoC (network-on-chip), vilket gör dem enkla att programmera för alla som arbetar med hårdvarukonstruktion och mjukvaruutveckling.

De nya funktionerna i Versal-enheterna inkluderar intelligenta motorer (en omfattande matris med vektorprocessorer för arbetslaster i form av maskininlärning och signalprocessning), stor bandbredd, låg latens och strömsnål programmerbar NoC som hanterar terabyte-volymer av data, integrerat gränssnitt som ger förbättrad prestanda, användning och produktivitet med färdig kärninfrastruktur och systemanslutningsbarhet.

En översikt över Versal ACAP-produkter visas i figur 5.

Figur 5: Xilinx Versal ACAP:er är mycket integrerade, flerkärniga plattformar som kan anpassa sig till olika och ständigt föränderliga algoritmer. ACAP:er är dynamiskt anpassningsbara vad gäller både hårdvara och mjukvara, vilket gör att de passar för många olika applikationer och belastningar. (Bildkälla: Max Maxfield)

Figur 5: Xilinx Versal ACAP:er är mycket integrerade, flerkärniga plattformar som kan anpassa sig till olika och ständigt föränderliga algoritmer. ACAP:er är dynamiskt anpassningsbara vad gäller både hårdvara och mjukvara, vilket gör att de passar för många olika applikationer och belastningar. (Bildkälla: Max Maxfield)

Som vi kommer att se i avsnittet med konstruktionsverktyg, är en viktig skillnad för Versal-enheter den nya mjukvarustacken för dataforskare och mjukvaruingenjörer, samt för ingenjörer som arbetar med traditionell hårdvarukonstruktion.

Det finns ett mycket stort utbud av Xilinx-enheter. Några representativa och intressanta erbjudanden är exempelvis Artix-7 FPGA, Kintex UltraScale FPGA, Kintex UltraScale+ FPGA, Zynq-7000 SoC-modul från Trenz Electronic GmbH och Zynq UltraScale+ MPSoC.

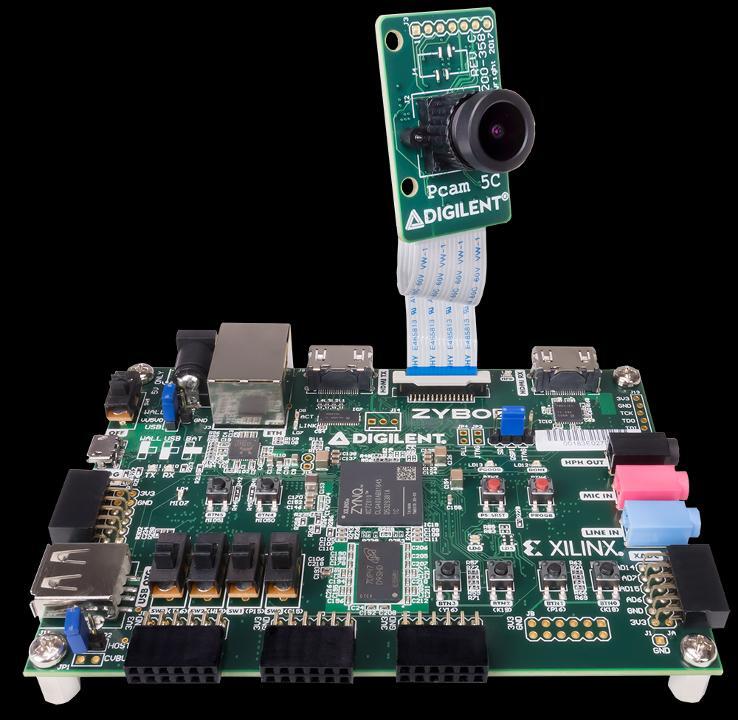

Det finns också många olika utvärderings- och utvecklingskort. Intressanta och representativa erbjudanden här är till exempel Artix-7 FPGA-utvärderingskort från Digilent, Kintex UltraScale FPGA-utvärderingskort från Analog Devices, Kintex UltraScale+ FPGA-utvärderingskort från Xilinx, Zynq-7000 SoC FPGA-utvärderingskort från Digilent och Zynq UltraScale+ MPSoC FPGA-utvärderingskort från Xilinx.

Konstruktion och utveckling med FPGA:er, SoC:er och ACAP:er från Xilinx

Ett område där Xilinx verkligen skiljer sig från mängden är när det gäller bredd och djup för deras konstruktionsverktyg och flöden.

I del 1 av denna serie om FPGA:er såg vi att det traditionella sättet att utforma dessa enheter är att ingenjörer använder ett hårvarubeskrivande språk (HDL) som Verilog eller VHDL för att förverkliga konstruktionen på en abstraktionsnivå känd som RTL (register transfer level). Dessa RTL-beskrivningar kan först simuleras för att säkerställa att de presterar som avsett och sedan överföras till ett syntesverktyg som genererar konfigurationsfilen som används för att programmera FPGA:n.

Nästa nivå av abstraktion är att förverkliga konstruktionsavsikten med ett programmeringsspråk som C/C++ eller en speciallösning som SystemC, vilken är en uppsättning C++-klasser och -makron som ger ett händelsestyrt simuleringsgränssnitt. Dessa underlättar simulering av samtidiga processer, var och en beskriven med vanlig C++-syntax. Sådana beskrivningar kan analyseras och profileras genom att de körs som regelbundna program och därefter skickas till en högnivåsyntesmotor (HLS), vilken matar ut RTL som matas in till en vanlig syntesmotor.

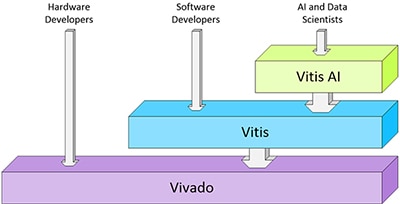

Alla dessa funktioner finns i Vivado Design Suite HLx Editions, från vilken konfigurationsbitströmmen som laddas till målenheten (FPGA, SoC, MPSoC, RFSoC eller ACAP) tillhandahålls. Förutom att ge hårdvaruutvecklare tillgång till C-baserad konstruktion och optimerad återanvändning, erbjuder Vivado också återanvändning av IP-subsystem, integrerad automation och uppsnabbad färdig konstruktion (design closure) (figur 6).

Figur 6: En högnivåvy över konstruktionsverktygen Xilinx Vivado och Vitis visar hur användare kan arbeta med verktygen på lämpligast möjliga abstraktionsnivå. Hårdvaruutvecklare arbetar med Vivado, mjukvaruutvecklare med Vitis och AI- och dataforskare med Vitis AI. (Bildkälla: Max Maxfield)

Figur 6: En högnivåvy över konstruktionsverktygen Xilinx Vivado och Vitis visar hur användare kan arbeta med verktygen på lämpligast möjliga abstraktionsnivå. Hårdvaruutvecklare arbetar med Vivado, mjukvaruutvecklare med Vitis och AI- och dataforskare med Vitis AI. (Bildkälla: Max Maxfield)

Nästa abstraktionsnivå stöds av Vitis Unified-mjukvaruplattformen, vilken ger mjukvaruutvecklare möjlighet att smidigt bygga accelererade applikationer. En nivå upp rent konceptuellt från Vitis finns Vitis AI, med vilken AI- och dataforskare kan arbeta på TensorFlow-abstraktionsnivå. Vitis AI är en utvecklingsplattform för AI-inferens på Xilinx hårdvaruplattformar, inklusive både gränsenheter och Alveo PCIe-kort. Den består av optimerad IP, verktyg, bibliotek, modeller och exempelkonstruktioner och är utformad för att utnyttja den fulla potentialen för AI-acceleration på Xilinx FPGA- och ACAP-enheter.

Vitis AI påverkar utvecklingen av Vitis, vilken i sin tur påverkar utvecklingen av Vivado. I figur 6 kan vi se hur användare bara ”ser” vad de behöver ”se”. Med det menar vi att hårdvaruutvecklare endast ser Vivado, att mjukvaruutvecklare endast ser Vitis och att AI- och dataforskare endast ser Vitis AI. På så sätt kan användare arbeta med verktyget på den lämpligaste abstraktionsnivån.

Med en verktygssvit som Vitis blir FPGA:er tillgängliga för många fler utvecklare, tack vare att de med den inte behöver hantera underliggande hårdvara. Och AI- och dataforskare får med en verktygssvit som Vitis AI möjlighet att fokusera på sin egen abstraktionsnivå och på så sätt isoleras från underliggande mjukvara, vilket gör FPGA:er tillgängliga för många fler utvecklare.

Med dessa möjligheter ställer sig Xilinx i framkant av en branschomfattande höjning av nivån för konstruktionsabstraktion i FPGA-verktyg, vilket gör att utvecklare enklare kan dra nytta av egenskaperna för dessa enheter och integrera dem i sina konstruktioner.

Slutsatser

Optimala processkonstruktionslösningar skapas ofta genom kombinationer av processorer och FPGA:er, genom FPGA:er på egen hand eller genom FPGA:er med interna processorkärnor. Tekniken som FPGA:erna bygger på har utvecklats snabbt under åren och uppfyller många konstruktionskrav när det gäller flexibilitet, databehandlingshastighet och prestanda. Detta gör dem mycket användbara i många olika tillämpningar – från intelligenta gränssnitt till maskinseende och AI.

Som vi har sett finns de programmerbara enheterna från Xilinx på alla nivåer, från enkla till mycket avancerade enheter vad gäller prestanda och egenskaper. De spänner från traditionella FPGA:er till SoC:er (FPGA-programmerbar struktur med en hård processorkärna), MPSoC:er (FPGA-programmerbar struktur med flera hårda processorkärnor), RFSoC:er (MPSoC:er med RF-kapacitet) och ACAP:er (Adaptive Compute Acceleration Platforms).

För att hjälpa utvecklare att bygga konstruktioner med hjälp av dessa enheter, har Xilinx tagit fram en verktygssvit som är anpassad för de behov som hårdvaruutvecklare (Vivado), mjukvaruutvecklare (Vitis) och AI- och dataforskare (Vitis AI) har.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.