Varför och hur man använder FPGA:er från Efinix för bildbehandling med AI/ML del 2: Bildtagning och bearbetning

Bidraget med av DigiKeys europeiska redaktörer

2023-05-05

Redaktörens anmärkning: Nya tillvägagångssätt för FPGA-arkitekturer ger en mer detaljerad styrning och en större flexibilitet för att tillgodose behoven för ML (maskininlärning) och AI (artificiell intelligens). Den första delen i denna tvådelade serie presenterar en sådan arkitektur från Efinix och hur man kommer igång med hjälp av ett utvecklingskort. Här, i den andra delen diskuteras gränssnittet mellan utvecklingskortet och externa enheter och kringutrustning, som t.ex. en kamera, och hur man utnyttjar FPGA:n för att ta bort flaskhalsar vid bildbearbetning.

Tillämpningar med FPGA:er spelar en mycket viktig roll i industriell styrning, säkerhet och robotteknik samt inom flyg- och fordonsindustrin. Det är tack vare flexibiliteten hos den programmerbara logikkärnan och dess många gränssnittsfunktioner som gör att ett ökande användningsområde för FPGA:er är bildbehandling, där maskininlärning (ML) kan användas. FPGA:er är tack vare sin parallella logiska struktur, perfekta för implementation i lösningar som har flera kameragränssnitt med hög hastighet. FPGA:er gör det dessutom möjligt att använda en dedikerad bearbetningspipeline i logiken, vilket eliminerar flaskhalsar för delade resurser, som skulle vara fallet med CPU-eller GPU-baserade lösningar.

Denna andra titt på FPGA:erna Titanium från Efinix kommer att undersöka referenstillämpningen för bildbearbetning som levereras med utvecklingskortet Ti180 M484 för FPGA:erna. Syftet är att förstå konstruktionens komponenter och att identifiera var teknologier med FPGA:er gör det möjligt att avlägsna flaskhalsar eller ge utvecklare andra fördelar.

Referenskonstruktionen är baserad på Ti180 M484

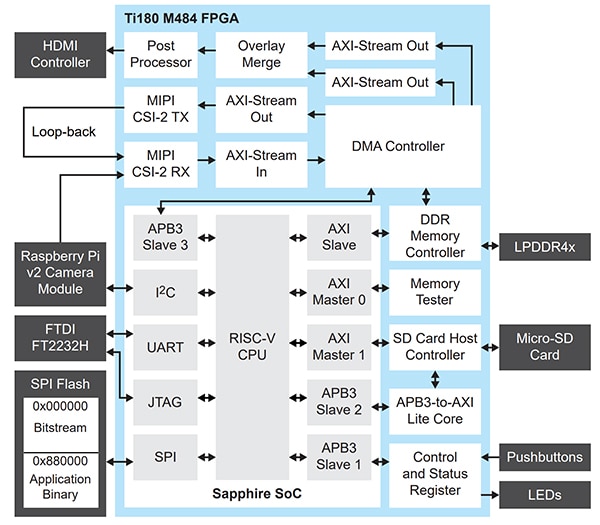

Referenskonstruktionen (figur 1) tar emot bilder från flera MIPI-kameror (Mobile Industry Processor Interface), utför bildbuffring i LPDDR4x och skickar sedan bilderna till en HDMI-skärm (High Definition Multimedia Interface). Ett FPGA Mezzanine Card (FMC) och fyra QSE-gränssnitt på kortet från Samtec används för att tillhandahålla kameraingångarna och HDMI-utgången.

Figur 1: Konceptuellt sett tar referenskonstruktionen Ti180 M484 emot bilder från flera MIPI-kameror, utför bildbuffring i LPDDR4x och skickar sedan ut bilderna till en HDMI-skärm. >(Bildkälla: Efinix)

Figur 1: Konceptuellt sett tar referenskonstruktionen Ti180 M484 emot bilder från flera MIPI-kameror, utför bildbuffring i LPDDR4x och skickar sedan ut bilderna till en HDMI-skärm. >(Bildkälla: Efinix)

Expansionskortet med FMC till QSE används tillsammans med tilläggskortet för HDMI för att tillhandahålla videoutgången medan tre QSE-kontakter används för att ansluta till MIPI-kamerorna SEN0494 från DFRobot. Om flera MIPI-kameror inte är tillgängliga kan en enda kamera användas genom att vända tillbaka den enda kamerakanalen för att simulera ytterligare kameror.

På en översiktlig nivå kan denna tillämpning verka enkel. Det är dock en utmaning att i hög bildhastighet ta emot flera högupplösta (HD) MIPI-dataströmmar. Det är här tekniken med FPGA:er är fördelaktig eftersom den gör det möjligt för konstruktörer att använda flera MIPI-strömmar parallellt.

Referenskonstruktionens arkitektur utnyttjar både parallella och sekventiella bearbetningsstrukturer med FPGA:n. De parallella strukturerna används för att implementera pipelines för bildbearbetning medan en RISC-V-processor tillhandahåller den sekventiella bearbetningen som används för FPGA:ns uppslagstabeller (LUT).

Pipelines för bildbearbetning kan i många bildbearbetningssystem baserade på FPGA delas upp i två delar, nämligen in- och utströmmarna. Inströmmen ansluts till gränssnittet för kameran/sensorn och bearbetningsfunktioner tillämpas på sensorns utgång. Funktionerna kan inkludera Bayer-konvertering, automatisk vitbalans och andra förbättringar. I utströmmen förbereds bilden för att visas. Detta inkluderar ändring av färgrymder (t.ex. RGB till YUV) och efterbearbetning för önskat dataformat, som t.ex. HDMI.

Utifrån bildbearbetningskedjan arbetar inkommande bilder oftast med sensorns pixelklockfrekvens. Den har en annan timing jämfört med utgångskedjan, som bearbetas vid skärmens utmatningsfrekvens.

En bildbuffert används för att ansluta ingången till pipelinen för utmatningsbearbetning, vilken oftast lagras i externa högeffektiva minnen, t.ex. LPDDR4x. Bildbufferten frånkopplas mellan pipelines för in och ut, vilket gör det möjligt att komma åt bildbufferten genom direkt minnesåtkomst vid lämplig klockfrekvens.

Referenskonstruktionen för Ti180 använder ett tillvägagångssätt likt de koncept som beskrivs ovan. Ingången med bildbearbetningspipelinen implementerar en IP (intellectual property)-kärna för en MIPI CSI-2 (Camera Serial Interface 2)-mottagare som bygger på den MIPI D-PHY-kompatibla in-/utgången (I/O) i FPGA:n från Titanium. MIPI är ett avancerat gränssnitt eftersom det använder både enkelbalanserad och dubbelbalanserad signalering i samma dubbelbalanserade par, utöver kommunikation med låg- och hög hastighet. Genom att integrera MIPI D-PHY i FPGA I/O:n minskar komplexiteten i kretskortets konstruktion samtidigt som materiallistan (BOM) minskas.

När bildströmmen från kameran har tagits emot omvandlar referenskonstruktionen utgången från MIPI CSI-2 RX till en AXI-ström (Advanced eXtensible Interface). En AXI-ström är ett enkelriktat höghastighetsgränssnitt som tillhandahåller en dataström från en master till en slav. Handskakningssignaler för överföring mellan en master och en slav tillhandahålls (tvalid och tready) tillsammans med sidobandssignaler. Sidobandssignalerna kan användas för att förmedla information om tider, t.ex. bildstart och radavslut.

AXI-strömmen är perfekt för bildbearbetningstillämpningar och gör det möjligt för Efinix att tillhandahålla en rad olika IP med bildbearbetning som sedan enkelt kan integreras i bearbetningskedjan enligt tillämpningens behov.

Efter mottagandet konverteras bildinformationen och tidssignaler från MIPI CSI-2 till en AXI-ström och matas in i en DMA-modul (direct memory access), som skriver bildrutan till LPDDR4x och fungerar som bildbuffert.

DMA-modulen styrs av RISC-V-kärnan i FPGA:n i en systemkrets (SoC) från Sapphire. Systemkretsen tillhandahåller styrning, t.ex. stopp och start av skrivning till DMA samt förser dessutom skrivkanalen för DMA med den information som krävs för att skriva bilddata till LPDDR4x på ett korrekt sätt. Detta inkluderar information om minnesplatsen och bildens bredd samt höjd definierat i bytes.

Utgångskanalen i referenskonstruktionen läser bildinformationen från bildbufferten i LPDDR4x med styrning från systemkretsen i RISC-V. Resultatet matas ut från DMA-IP:n som en AXI-ström, som sedan konverteras från RAW-formatet, som tillhandahålls av sensorn, till RGB-format (figur 2) och förbereds för utmatning via den inbyggda HDMI-sändaren ADV7511 från Analog Devices.

Figur 2: Bildexempel från referenskonstruktionen. (Bildkälla: Adam Taylor)

Figur 2: Bildexempel från referenskonstruktionen. (Bildkälla: Adam Taylor)

Användningen av DMA gör det även möjligt för systemkretsen RISC-V från Sapphire att få tillgång till de bilder som lagras i bildbufferten samt till abstrakt statistik och bildinformation. Systemkretsen från Sapphire kan även skriva överlappande till LPDDR4x så att de kan sammanfogas med den utgående videoströmmen.

Moderna CMOS-bildsensorer (CIS) har flera olika driftssätt och kan konfigureras för att tillhandahålla inbyggd bearbetning i kretsen, samt flera olika utdataformat och klockningsscheman. Denna konfiguration tillhandahålls normalt via ett I²C-gränssnitt. I referenskonstruktionen från Efinix tillhandahålls denna I²C-kommunikation till MIPI-kamerorna av RiSC-V-processorn i systemkretsen Sapphire.

Integreringen av RISC-V-processorn i FPGA:n från Titanium minskar den totala storleken på den slutliga lösningen eftersom den eliminerar behovet av att implementera både komplicerade tillståndsmaskiner med FPGA som ökar konstruktionsrisken samt externa processorer som ökar på materiallistan.

Processorn möjliggör även stöd för ytterligare IP för att kommunicera med MicroSD-kortet. Detta möjliggör verkliga tillämpningar där bilder kan behöva lagras för att analyseras senare.

Referenskonstruktionens arkitektur för Ti180 är optimerad för att möjliggöra en kompakt och billig, men ändå högeffektiv, lösning som gör det möjligt för utvecklare att minska kostnaden för materiallistan genom systemintegration.

En av de viktigaste fördelarna med referenskonstruktioner är att de kan användas för att snabbt starta utvecklingen av tillämpningar på anpassad hårdvara, vilket gör det möjligt för utvecklare att ta viktiga delar av konstruktionen och bygga vidare på den med de anpassningar de behöver. Detta inkluderar möjligheten att använda TinyML-flöden från Efinix för att implementera bildbaserade tillämpningar med TinyML som körs på FPGA:n. Både FPGA-logikens parallella natur och förmågan att enkelt lägga till anpassade instruktioner i RISC-V-processorer kan utnyttjas, vilket gör det möjligt att skapa acceleratorer inom logiken för FPGA.

Implementation

Som diskuterades i första delen är arkitekturen från Efinix unik eftersom den använder XLR-celler (eXchangeable Logic and Routing) för att tillhandahålla funktioner för både routning- och logik. Ett videosystem som exempelvis referenskonstruktionen är ett blandat system som är både logik- och routningkrävande; det krävs omfattande logik för att implementera funktioner för bildbearbetning samt omfattande routning för att ansluta IP-cellerna vid de erfoderliga frekvenserna.

Referenskonstruktionen använder cirka 42 % av XLR-cellerna i enheten vilket ger gott om utrymme för tillägg, inklusive anpassade tillämpningar som t.ex. Edge ML.

Användningen av RAM-blocket och DSP-blocken (digital signalbehandling) är också mycket effektiv; endast 4 av de 640 DSP-blocken och 40 % av minnesblocken används (figur 3).

|

Figur 3: Resursallokering i arkitekturen från Efinix visar att endast 42 % av XLR-cellerna används, vilket ger gott om utrymme för ytterligare processer. (Bildkälla: Adam Taylor)

På enhetens I/O används DDR-gränssnittet för LPDDR4x för att tillhandahålla programminne för systemkretsen från Sapphire och buffertar för bildrutor. Alla MIPI-resurser som dedikerats för enheten används tillsammans med 50 % av faslåsningslooparna (figur 4).

|

Figur 4: Stillbild på gränssnittet och de I/O-resurser som används. (Bildkälla: Adam Taylor)

GPIO (General Purpose I/O) används för att tillhandahålla I²C-kommunikation tillsammans med flera av de gränssnitt som är anslutna till systemkretsen från Sapphire, inklusive NOR FLASH, USB UART och SD-kort. HSIO används för att skapa en höghastighetsutgång för video till HDMI-sändaren ADC7511.

Vid konstruktioner med FPGA:er är det inte bara att implementera och anpassa konstruktionen i FPGA:n, utan det är även viktigt att att kunna placera logikkonstruktionen i FPGA:n och uppnå den prestanda för timing som krävs när den styrs.

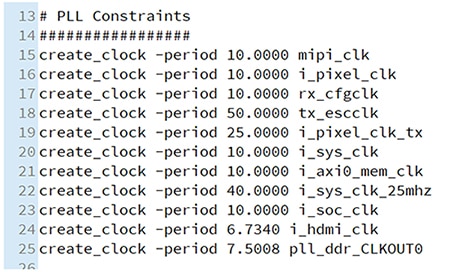

Sedan länge är dagarna med FPGA-konstruktioner som endast har en klockdomän förbi. Det finns flera olika klockor som alla körs med höga frekvenser i referenskonstruktionen för Ti180. Den avslutande tabellen visar de maximala frekvenser som uppnåtts för klockorna i systemet. Det är här som den begärda timingprestandan också kan ses i begränsningarna (figur 5), som har en maximal klockfrekvens på 148,5 MHz för HDMI-utgångens klocka.

Figur 5: Referenskonstruktionens klockbegränsningar. (Bildkälla: Adam Taylor)

Figur 5: Referenskonstruktionens klockbegränsningar. (Bildkälla: Adam Taylor)

Implementering av timing mot begränsningarna visar potentialen hos FPGA XLR-strukturen från Titanium eftersom den minskar den möjliga fördröjningen i routningen och ökar därmed konstruktionens prestanda (figur 6).

|

Figur 6: Implementering av timing för att motverka begränsningarna visar potentialen hos FPGA XLR-strukturen från Titanium för att minska den möjliga fördröjningen i routningen och därmed öka konstruktionens prestanda. (Bildkälla: Adam Taylor)

Sammanfattning

Referenskonstruktionen Ti180 M484 visar tydligt upp kapaciteten hos FPGA:er från Efinix och då särskilt Ti180. Konstruktionen utnyttjar flera av de unika I/O-strukturerna för att implementera en komplicerad väg för bildbearbetning som stöder flera inkommande MIPI-strömmar. Detta bildbearbetningssystem styrs av en mjuk kärna med systemkretsen från Sapphire som implementerar de nödvändiga sekventiella bearbetningselementen för tillämpningen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.