Varför och hur ett programminne på mikrosstyrenhet utökas bäst med SPI XiP Flash

Bidraget med av DigiKeys nordamerikanska redaktörer

2019-05-08

Tillämpningarna med mikrostyrenheter blir alltmer komplexa och utvecklarna behöver därmed också använda mer flashprogramminne för tillämpningens fasta programvara. Detta gäller särskilt för slutpunkter inom sakernas internet (IoT) som börjar utföra relativt avancerade kantberäkningar. Ibland utökas dock en del tillämpningar så mycket att ett externt programminne behövs. I sådana fall måste utvecklarna välja mellan parallellt eller seriellt flashminne.

Om ett externt parallellt flashminneschipp läggs till binds fler I/O-linjer upp, och konstruktionen blir mer komplex och kräver extra utrymme på kortet. I den här artikeln beskriver vi hur flashprogramminnet på en styrenhet kan utökas genom tillägg av ett externt seriellt Flashminneschipp från Adesto Technologies som har stöd för ett SPI eXecute in Place (XiP)-gränssnitt. Den förklarar även hur XiP Flash mappas till minnesutrymmet på en Microchip Technology-mikrosstyrenhet, så att kodkörningen blir nästan transparent till den fasta programvaran.

Orsaker till att utöka det externa minnet

Om möjligt bör utvecklare börja utveckla tillämpningen med att välja mikrostyrenheter som har utvecklingsplaner för utökat minne via enheter med kompatibla stift. Om den fasta programvaran börjar växa under utvecklingen av tillämpningen, så att flashminnet på målenheten inte längre räcker till, är det lätt att byta till en enhet med kompatibla stift och mer Flashminne under utvecklingen. Då kan tillämpningens minne utökas utan att PC-kortet måste designas om för en annan mikrostyrenhet.

Tillämpningen kan dock behöva mer programminne än vad som finns tillgängligt på chippet för en mikrostyrenhet med kompatibla stift, vilket innebär att ett flashminne utanför chippet måste användas. Det här blir allt vanligare och det kan ha flera orsaker, bland annat:

- Systemomfattningen kan vidgas utöver det initiala konceptet under utvecklingsfasen. Det kan bero på sista minuten-ändringar i tillämpningen, att funktioner växer ut eller tillämpningens behov av minne inte förutsågs korrekt. Alternativen blir då att antingen uppgradera med en styrenhet med kompatibla stift och som har mer flashprogramminne eller lägga till ytterligare externt flashprogramminne, vilket kan försena projektet om utvecklingsarbetet redan är långt gånget.

- Framtida uppgraderingar av den fasta programvaran kan kräva mer flashprogramminne än vad som finns tillgängligt på den mikrostyrenhet som redan sitter på systemkortet. I denna situation är alternativen begränsade: antingen kan systemen på fälten bytas ut mot nya med mer flashprogramminne eller också måste uppgraderingen annulleras.

- Utvecklingen av systemets produktfamilj kan kräva en ny produkt som behöver mer flashprogramminne än vad som redan finns tillgängligt för familjen med mikrostyrenheter med kompatibla stift. Då återstår alternativen att omdesigna systemet med en ny mikrostyrenhetsfamilj eller också lägga till externt flashprogramminne.

Självklart är det viktigt för en utvecklare att kunna förutse vilka behov som ställs av dagens och framtidens system när det gäller minnesutökning, och att ta höjd för den i sin planering. Om det finns en möjlighet att projektet kommer att behöva externt flashprogramminne, måste utvecklaren se till att det finns plats för framtida utbyggnad på PC-kortet i sin layout. Flashminneschippet behöver inte verkligen finnas där på kortet, men det är bättre att vara på den säkra sidan och se till att det finns plats i layouten.

Det traditionella sättet att utöka flashprogramminne är att använda ett parallellt flashgränssnitt med adress och datalinjer. Nackdelen är dock även vid mycket effektiv användning av parallellt Flashminne där hastigheten är hög, används 16 bitar för adressen, 16 bitar för data, och fyra eller fler för kontrollsignaler. Detta kräver 36 eller fler stift på mikrostyrenheten.

Det är inte bara ett ineffektivt sätt att använda resurserna för en mikrostyrenhet, det begränsar också valet av mikrostyrenhet till enheter som har en extern buss, vilket i sin tur ökar antalet stift på mikrostyrenheten. En extern parallell buss tar också upp betydande plats på PC-kortet, medan en höghastighets adress- och databuss ökar risken för elektromagnetiska störningar.

Körning av SPI XiP-kod

Ett effektivare alternativ är att använda en extern flashprogramminnesenhet med stöd för SPI XiP-gränssnitt. Ett SPI XiP-gränssnitt behöver bara sex stift för att kommunicera med mikrostyrenheten som fungerar som värd. Till skillnad från konventionella SPI-gränssnitt, nås minnet på den externa flashminnesenheten inte med hjälp av en drivrutin i den fasta SPI-programvaran, utan mappas i mikrostyrenhetens programminne.

Ett bra exempel på en seriell flashminnesenhet avsedd för användning av SPI XiP-gränssnittet, är AT25SL321-UUE-T från Adesto Technologies (figur 1). Det här är ett Flashminne på 32 megabit (Mbit) med stöd för enkla, dubbla och fyrdubbla SPI-lägen. Den ger stöd till en SPI-klocka på 104 megahertz (MHz), vilket i dubbelt SPI-läge ger en motsvarande klockfrekvens på 266 MHz, och i fyrdubbelt SPI-läge en motsvarande klockfrekvens på 532 MHz.

Figur 1: Adesto AT25SL321 är ett Flashminne på 32 megabit (Mbit) med stöd för enkla, dubbla och fyrdubbla SPI-lägen. Det ger 32 Mbit Flashminne i ett 8-stifts SOIC-, DFN8- eller TSSOP8-paket. (Bildkälla: Adesto Technologies)

Förutom 32 Mbit Flashminne har enheten statusregister för konfigurering av enheten. Genom avläsning av statusregistren kan den fasta programvaran ta reda på om enheten har en pågående skriv- eller raderingsåtgärd. Eftersom det går att skriva till statusregistren kan block med Flashminne skrivskyddas.

Adesto AT25SL321 har även 4 kb (kilobit) OTP-minne (minne som kan programmeras en gång) för lagring av säkerhetsinformation såsom ett unikt serienummer. Den levereras i ett 8-stifts SOIC-, DFN8- eller TSSOP8-paket.

I likhet med alla seriella minnesenheter som har stöd för SPI XiP konfigureras Adesto AT25SL321 med hjälp av en uppsättning instruktioner som är specifika för Adesto-enheter. Instruktionsuppsättningen består av 38 kommandon som används av värdmikrostyrenheten för att styra den seriella flashenheten. En perifer SPI XiP-enhet på en värdmikrostyrenhet innehåller en programmerbar finit automat som initieras när mikrostyrenheten strömsätts med den instruktionsuppsättning som finns i det seriella målflashminnet. Efter initieringen körs den perifera SPI-enheten transparent till körning av koden i den fasta programvaran i den minnesmappade SPI XiP-regionen.

Om värdmikrostyrenhetens fasta programvara till exempel läser data från den minnesmappade regionen, kommer den SPI XiP som konfigurerats med Adestos instruktionsuppsättning att skicka en instruktion om att läsa data åtföljd av en 24-bitars byteadress till det seriella Adesto-minnet. Det seriella Adesto-minnet skickar därefter minnesinnehållet till värdmikrostyrenheten en byte i taget. För den fasta programvaran visas detta som en normal läsning från minnet.

Adesto AT25SL321 har vid sidan av en SPI-klocka, data och valbara chippstift, även två extra stift som gör användbarheten i systemet ännu större. WP\ är ett stift som skyddar aktivt mot skrivning till statusregistret för att skrivskydda kodblock. Mikrostyrenheten kan använda det här stiftet för att skydda uppgifter med låg prioritet från att göra obehöriga ändringar. HOLD\ används för att pausa en pågående dataöverföring. Det kan vara användbart om mikrostyrenheten tar emot en avbrottssignal med hög prioritet medan en dataöverföring håller på att utföras till minnet, och denna måste pausas tills avbrottet har hanterats.

Adesto AT25SL321 32 Mbit flashenhet har stöd för fyra driftlägen:

- Standard SPI-drift: Flashminnet används standardenligt som en SPI-minnesenhet med SPI-klocka (SCLK), active-low chip select (CS\), seriell inmatning (SI) av data och seriell utmatning (SO) av data. Standard SPI-busslägena 0 och 3 stöds.

- Dubbel SPI-drift: Det här läget ger dubbla datahastigheten jämfört med Standard SPI genom att SI och SO används som dubbelriktade datastift, betecknade IO0 och IO1.

- Fyrdubbel SPI-drift: Det här läget ger fyrdubbla datahastigheten jämfört med Standard SPI. Förutom IO0 och IO1 används WP\ och HOLD\ som dubbelriktade datastift, nämligen IO2 och IO3. I fyrdubbel SPI-drift går det inte använda funktionerna WP\ och HOLD\.

- QPI-drift: Används endast med SPI XiP-drift. I lägena standard, dubbel och fyrdubbel SPI-drift finns det stöd för att skicka kommandon till SPI-minnet enbart med IO0-stiftet medan QPI-drift har stöd för att skicka kommandon med de fyra IO[0:3]-stiften, vilket ger betydligt ökad prestanda för SPI XiP.

Om 32 Mbit för Adesto AT25SL321 inte räcker, finns även en 64 Mbit AT25QL641-UUE-T från Adesto. De två enheterna har kompatibla stift, så det är väldigt enkelt att byta till en AT25QL641. Förutom att den ena har mer minne, är den enda skillnaden mellan de två enheterna att AT25QL641 är inställd på QPI-drift som standard vid start. Det reducerar inställningstiden för enheten i system med hög kapacitet. Båda drar enbart 5 milliamp (mA) per minnesläsningscykel. Bägge minnesenheterna från Adesto fungerar från en skena med 1,7 till 2,0 volt, och har ett gränssnitt som fungerar med alla spänningskompatibla mikrostyrenheter som har ett SPI XiP-gränssnitt.

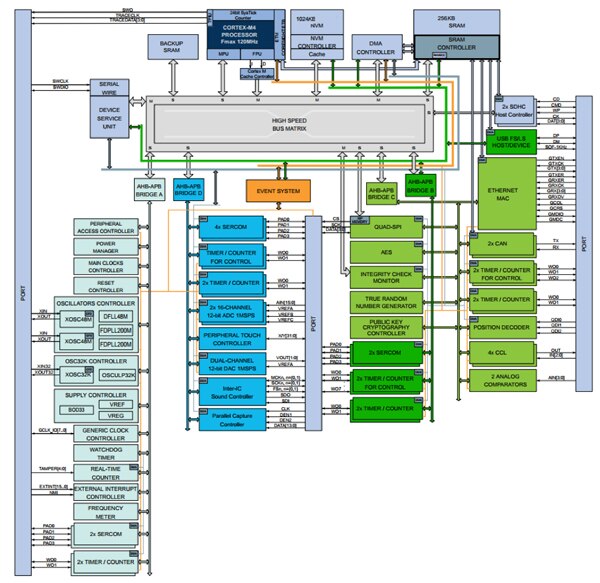

För värdmikrostyrenheten har Microchip Technology SPI XiP-gränssnitt på sin ATSAMD51-serie, där bland annat den 120 MHz Arm® Cortex®-M4F-baserade mikrostyrenheten ATSAMD51J20A-UUT kan lyftas fram. Denna enhet har 1 Mbyte Flash och 256 kilobyte (Kbyte) RAM. Utbudet av kringutrustning är komplett, med bland annat en analog-till-digitalomvandlare (ADC), digital-till-analogomvandlare (DAC), USB-port och I2S. Bland säkerhetsfunktionerna kan nämnas kryptering med allmän nyckel och en äkta slumpnummergenerator (TRNG).

Figur 2: Microchip ATSAMD51J20A har en komplett kringutrustning, med bland annat ett seriellt SPI XiP-gränssnitt, ADC, DAC samt stöd för datakryptering. (Bildkälla: Microchip Technology)

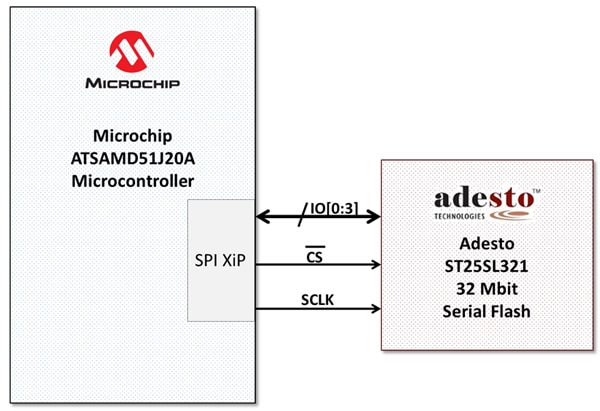

För anslutning till det externa Flashminnet kan utvecklare använda den perifera QSPI-enheten till ATSAMD51J20A som har stöd för SPI XiP. Det gör att kod kan köras direkt från Adesto-flashminnet. ATSAMD51J20A mappar Adesto-flashminnet med Arms Advanced High-Performance Bus (AHB) programminnesutrymme. För att skydda data i det seriella flashminnet har ATSAMD51J20A SIP XiP stöd för transparent kryptering av data som skrivits till ett externt SPI-minne och dekryptering av data som lästs in från ett externt SPI-minne. Det kan bidra till att förhindra oönskad kopiering av fast programvara och piratangepp på systemet.

Figur 3: Microchip ATSAMD51J20A 32-bitars mikrostyrenhet har en QSPI-enhet som har stöd för en seriell SPI XiP-port. Den är lätt att använda med Adesto AT25SL321 seriellt flashminne med endast sex stift. (Bildkälla: DigiKey)

Använda Microchip ATSAMD51J20A med en Adesto seriell flashminnesenhet

Microchip ATSAMD51J20A SPI XiP-enhet har tre register som används för att skicka kommandon till ett externt seriellt XiP flashminne. Eftersom seriella Flash XiP-minnesenheter från olika leverantörer använder olika instruktionskoder måste dessa register konfigureras enligt följande av utvecklaren för den specifika minnesleverantören som används:

- Instruktionskodregistret innehåller instruktionerna som används för att komma åt det seriella flashminnet. För en Adesto flashminnesenhet i fyrdubbelt SPI-läge innehåller det här registret en Fast Read Quad Output-instruktion 0x6B om fast programvara kör kod utanför den minnesmappade XiP-regionen. Registret måste ändras till den lämpliga instruktionskoden om en skriv- raderings- eller statusregisteråtgärd utförs.

- Instruktionsadressregistret innehåller flashminnesadressen som används i det externa seriella flashminnet. När Microchip ATSAMD51J20A SPI XiP är konfigurerat för seriellt minnesläge ställs den här adressen automatiskt in av den perifera SPI XiP-enheten på adressen som körs i den fasta programvaran i minnet som mappat AHB-minnesutrymmesintervallet 0x0400 0000 till 0x0500 0000.

- Instruktionsramregistret konfigurerar SPI XiP för instruktionsramformatet som är specifikt för den externa minnesenheten som används. Det omfattar att välja adresslängden på 24 eller 32 bitar, aktivera DDR (double-data rate), om läget för kontinuerlig läsning stöds och operationskodslängden.

Resten av Microchip SPI XiP-gränssnittet är enkelt att konfigurera med Microchip SPI-drivrutiner.

Så länge som tillämpningens fasta programvara på mikrostyrenheten kör kod från den SPI XiP-minnesmappade region behöver den perifera SPI XiP-enheten på mikrostyrenheten inte omkonfigureras. Adesto flashminnet har även stöd för ett läsläge med endast ett SI-stift med instruktionskoden 0x03. Om endast dubbelt SPI-läge används är instruktionskoden 0x3B. Dessa koder skrivs av tillämpningens fasta programvara till instruktionskodsregistret.

Det anses vara en god rutin att tömma alla cacheminnen som är kopplade till minnesmappat adressområde när instruktionskodsregistret ändras. När du läser eller skriver till det seriella flashminnets statusregister ska cacheminnet tömmas och sedan inaktiveras. Det ska även göras när det skrivs till flashminne i de minnesmappade regionerna. Cacheminnet ska återaktiveras när minnesläsåtgärder återupptas.

På grund av de snabba dataöverföringarna ska det seriella flashminnet sitta så nära som möjligt till mikrostyrenhetens SPI XiP-port på PC-kortet. Om det inte går ska spår inte vara längre än 120 millimeter (mm). Klocksignalen ska vara minst tre gånger bredden på PC-kortets spår från andra signaler för att undvika störningar. IO[0:3] dubbelriktade datasignaler ska alla vara inom 10 mm från varandra för att undvika förskjutning.

Slutsatser

Externa seriella flashminnesenheter kan ge snabb körning av fast programvara utan komplexitet och extra kortutrymme för parallella flashchipp. Det möjliggör enkel expansion av programkod över tid samt fältuppdateringar utan omdesign av systemkortet.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.