Använda Flashless-mikrostyrenheter för att sänka systemkostnader och öka prestanda

Bidraget med av DigiKeys nordamerikanska redaktörer

2019-08-22

Då IoT-nätverk (Internet of Things – Sakernas internet) ska utföra mer komplicerade uppgifter har minneskraven för IoT-slutpunkter ökat, särskilt för slutpunkter som nu utföra högre nivåer av edge-databehandling. Men ett Flash-minne med onchip-mikrostyrenhet är begränsat till cirka 1 Mbit och många högkvalitativa IoT-slutpunkter behöver många gånger större minne än så.

Den konventionella lösningen har varit att utöka mikrostyrenhetens programminne med ett externt Flash-chip. Men när minneskraven är så höga som 8 Mbit eller mer läggs till slut det mesta av programminnet offchip.

Därför är det i många fall bättre för konstruktörer att helt göra sig av med onchip-Flashminnet helt och istället använda en Flashless-mikrostyrenhet, eller ROMless-mikrostyrenhet, tillsammans med ett oktalt SPI eXecute-in-place (XiP)-Flash-chip med hög hastighet. Det ger en betydligt lägre kostnad för mikrostyrenheten och framtidssäkrar designen genom större skalbarhet. Eventuella problem med minnesåtkomsttider hanteras med de oktala minnesgränssnitten med mycket hög hastighet.

I den här artikeln diskuteras ROMless-mikrostyrenheter och externa minnen, och deras utveckling till ett livskraftigt alternativ för IoT-slutpunkter och inbäddade system som kräver stora mängder programminne. Därefter visas hur konceptet tillämpas med hjälp av ROMless-mikrostyrenheter från NXP Semiconductors och ett oktalt SPI XiP-Flash-chip från Adesto Technologies.

Minnesexpansion vid IoT-gränsen

De flesta IoT-slutpunkter med låga eller medelhöga prestanda använder en mikrostyrenhet för att hantera slutpunkten, och den fasta programvaran lagras på onchip-Flash. Den fasta programvaran utökas då det läggs till ytterligare programkod, stackar för trådlös IP-kommunikation och förbättrad säkerhetskod. Kodexpansion kan ske i utvecklingsfasen och som ett resultat av fältuppdateringar.

Vissa av dessa IoT-slutpunkter ska nu utföra fler databehandlingsfunktioner. Istället för att överföra råa eller delvis bearbetade sensordata över nätverket till en centraldator för bearbetning utför dessa IoT-slutpunkter mer komplexa uppgifter som kan omfatta sensorfusionsalgoritmer, datainterpolering, mönster- eller bildigenkänning och alltmer komplex AI-databehandling.

Eftersom detta resulterar i att centraldatorn bara får resultatet från IoT-nodens lokala bearbetning istället för varje byte av de råa sensordata kan detta leda till minskad trafik på det trådlösa nätverket. Eftersom RF-sändaren kan vara det best betydande effektförbrukaren i en IoT-slutpunkt resulterar edge-databehandling ofta i bättre batterilivslängd för batteridrivna slutpunkter.

System som måste uppdateras på fältet har fler utmaningar när det gäller minne. Konventionella system kräver minst dubbelt så mycket beräknat programminnesutrymme för att kunna hantera sådana uppdateringar. Detta för att kunna hantera både det befintliga programminnet och storleken på fjärruppdateringar. Vissa system kan kräva tre gånger så mycket programminnesutrymme, med det extra minnet tilldelat till en skrivskyddad fabriksavbildning med fast programvara. Vid vissa fall av systemfel, till exempel om hackning eller en skadad avbildning av fast programvara upptäcks, kan systemet läsa in den första fabrikslevererade fasta programvaran för att återställa systemet.

För vissa tillämpningar kan det här minnet snabbt överstiga 1 Mbit-gränsen för inbäddad Flash, vilket kräver utökat externt minne. Traditionellt har lösningen varit att lägga till ett externt parallellt Flashminneschip. Men nackdelen men det är att du måste använda cirka 36 externa stift på mikrostyrenheten – stift som annars kan användas för tillämpningens I/O. Det här slösar även PC-kortutrymme och ökar sannolikheten för elektromagnetiska störningar (EMI) från kortet.

Expansion av SPI-programminne

Förutom att använda en parallell buss kan programminne också utökas med hjälp av SPI (Serial Peripheral Interface). Det konventionella SPI använder bara en datarad för enkelbitsöverföringar med halv duplex, men under åren har det vuxit för att stödja dubbla och fyrdubbla datarader, vilket resulterat i en motsvarande ökning i datagenomströmning. Den här genomströmningen har ökat till en punkt där det har blivit praktiskt att använda ett externt SPI Flash-chip med stor kapacitet som gränssnitt.

För programminnestillämpningar använder ett konventionellt dubbel- eller fyrdubbel-SPI en konfiguration med skugg-Flash där det externa Flash-dataminnet kopieras till ett inbäddat SRAM-minne som mappas till programminnesutrymme. Fördelen med detta är att det är enkelt att utöka programminnet och samtidigt förbättra körningshastigheten genom att förbruka snabbt SRAM-minne, men det finns även betydande nackdelar. Eftersom mängden internt SRAM-minne är begränsat används minnet i ett sidindelat läge då Flashminnet byts till internt SRAM-minne efter behov. Den här flaskhalsen kan motverkas genom att lägga mer SRAM på chippet, men eftersom SRAM-minne är ett av de dyraste blocken på halvledare är nackdelen att mikrostyrenheten blir mycket dyrare.

En nyare utveckling för SPI är XiP. Med SPI XiP kan mikrostyrenhetens processor köra fast programvara-kod direkt från det externa SPI-Flashminnet. Programkörningshastigheten kan förbättras betydligt genom att lägga till en cache i SPI XiP-gränssnittet.

Populariteten hos SPI XiP har lett till en nylig utbyggnad av gränssnittet med åtta datarader. Det här oktala SPI XiP-gränssnittet har ökat genomströmningen till en punkt där det är mycket snabbare än att köra från onchip-Flashminne – snabbare än 100 Mbit/s.

SPI-minnesrevolution

Det här har lett till en lustig utveckling som kastar oss tillbaka 30 år i tiden. Tänk på ett system där det finns 1 Mbit onchip-Flash och 32 Mbit extern Flash som programminne som används av ett oktalt SPI XiP-gränssnitt. Onchip-programminnet är så minimalt så att följande fråga är självklar: Kan det onchip-Flashminnet för mikrostyrenheten tas bort och systemet ändå vara kostnadseffektivt?

Det har länge antagits att ett system i mellanskiktet med Flash-mikrostyrenhet alltid är mer kostnadseffektivt än ett med en Flashless-mikrostyrenhet med ett externt Flash-chip. Det här har bara nyligen ändrats.

Om onchip-Flashminnet tas bort minskas såklart kostnaden för mikrostyrenheten. Men en närmare undersökning visar att om Flashminnet inte längre behövs kan processteknikfunktionerna som bara används för Flash också tas bort. Det här minskar kostnaderna för tillverkningsprocessen, vilket ger en betydligt lägre kostnad för mikrostyrenheten. Det här har lett till återkomsten av något som för 30 år sedan kallades för ”ROMless” mikrostyrenhet. Idag kallar vi det Flashless.

(Åter)introduktion till Flashless-mikrostyrenheter

En mikrostyrenhet med höga prestanda som kan utnyttja Flashminnets hastighet är Flashless MIMXRT1052DVL6B (RT1052) från NXP Semiconductors. RT1052 är en medlem i NXP:s i.MX RT1050-processorsfamilj och baseras på 600 megahertz (MHz) Arm® Cortex®-M7 med 32 kB instruktionscache och 32 kB datacache. 600 MHz klockhastighet uppnås genom att ta bort Flashminne och använda en höghastighets CMOS-processteknik som inte har begränsats av internt Flashminne. RT1052 har en stor mängd SRAM-minne – 512 kilobyte (kB) – som kan partitioneras för program- eller dataminnesanvändning.

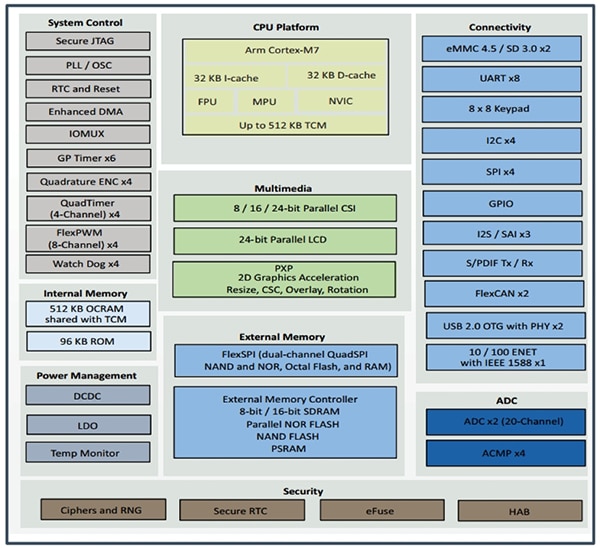

Mikrostyrenheten har flera olika avancerade kringutrustningsenheter, inklusive ett LCD-gränssnitt, ett digitalt kamerasensorsgränssnitt (CSI) och en pixelbearbetningspipeline (PXP) för avancerat kamerastöd, ett SPDIF-gränssnitt för digitalt ljud, två USB OTG-gränssnitt, två eMMC/SD Flash-kortgränssnitt, två 20-kanalers analog-till-digitalomvandlare (AD-omvandlare) samt en krypteringsmodul. En komplett lista över kringutrustning visas i blockdiagrammet (figur 1).

Figur 1: NXP RT1052 har en bred uppsättning avancerad kringutrustning, bland annat ett seriellt SPI XiP-gränssnitt och stöd för datakryptering. (Bildkälla: NXP)

Figur 1: NXP RT1052 har en bred uppsättning avancerad kringutrustning, bland annat ett seriellt SPI XiP-gränssnitt och stöd för datakryptering. (Bildkälla: NXP)

Ett annat alternativ är NXP MIMXRT1051DVL6B (RT1051). Det har samma funktioner som RT1052, minus LCD-gränssnittet, CSI och PXP.

RT1052 har ett FlexSPI-gränssnitt, som kan köra kod med dubbla, fyrdubbla eller oktala SPI XiP Flash-gränssnitt. För extra säkerhet för fast programvara stöder mikrostyrenheten krypterat programminne via SPI XiP. Ett bra exempel på detta är ATXP032-CCUE-T från Adesto Technologies.

Modern XiP Flash-funktion

Adestos ATXP032-CCUE-T är ett 32 Mbit oktalt Flash-chip som stöder dataöverföringar på upp till 266 megabyte (MB) per sekund i oktalt DTR-läge (dual transfer rate) – mycket snabbare än onchip-Flashminne för mikrostyrenheter. Det kräver en enda 1,8 V-försörjning och har en typisk standby-ström för oktalt läge på 35 mikroampere (µA). Det stöder en maximal SPI-klocka på 133 MHz.

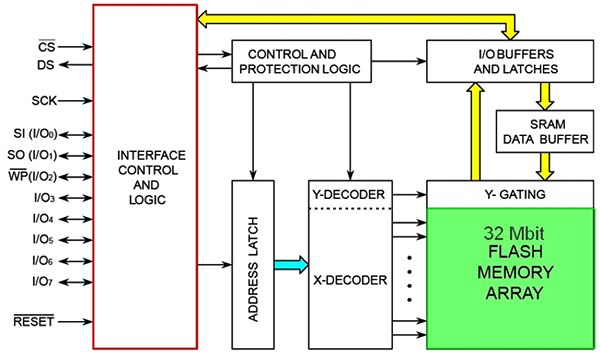

Figur 2: Adesto ATXP032-CCUE-T Flashminne använder ett oktalt SPI, I/O0 till I/O7, för att samverka med en mikrostyrenhet. En SRAM-skrivdatabuffert förbättrar prestandan för skriva-till-Flash-åtgärder. (Bildkälla: Adesto Technologies)

Figur 2: Adesto ATXP032-CCUE-T Flashminne använder ett oktalt SPI, I/O0 till I/O7, för att samverka med en mikrostyrenhet. En SRAM-skrivdatabuffert förbättrar prestandan för skriva-till-Flash-åtgärder. (Bildkälla: Adesto Technologies)

Under en aktiv Flash-läsning är strömförbrukningen för ATXP32 142 µA/MHz plus 1 milliampere (mA) overhead (typiskt). Vid högsta SPI-klockhastighet på 133 MHz i oktalt läge förbrukar det bara 19,9 mA.

ATXP032-CCUE-T stöder även SPI-standardlägena 0 och 3 samt fyrdubbelt SPI-läge. Ett säkerhetsregister på 256 byte har en fabriksprogrammerad unik identifierare på 128 byte och ett OTP-minne (one-time programmable – minne som kan programmeras en gång) på 128 byte som kan användas för att lagra enhetsinformation som en Ethernet MAC-adress eller en säkerhetsnyckel.

ATXP032-CCUE-T:s minnesarrangemang är värt att notera. Det är partitionerat i fyra banker på 8 Mbit vardera. Den interna logiken är konfigurerad så att en värdmikrostyrenhet kan köra kod från en bank och samtidigt programmera eller radera en annan. Funktionen är transparent för värdmikrostyrenheten och kräver inga särskilda konfigurationsinställningar.

ATXP032-CCUE-T har även tre status- och kontrollregister för att konfigurera driftsparametrarna för enheten som lågeffektsläge, aktivera eller inaktivera DTR-läge, och ange standard, fyrdubbelt eller oktalt SPI-läge (standard SPI är standardinställningen). Läsning från statusregistren kan ange statusen för en programmerings- eller raderingsåtgärd, lågeffektstatusen och om något minne är skrivskyddat.

Kombinera Flashless-mikrostyrenheter och extern XiP

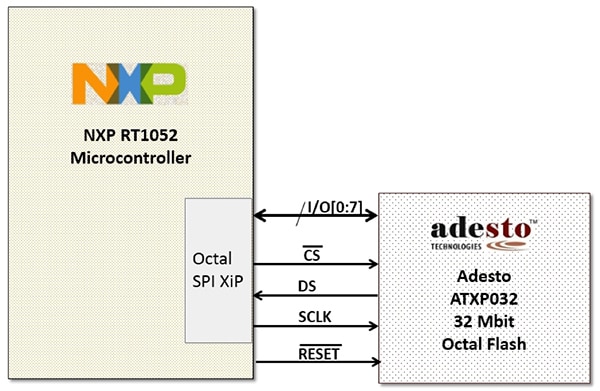

Det är enkelt att kombinera RT1052 och ATXP032-CCUE-T (figur 3). Vid start börjar RT1052 köra kod utifrån de 96 kB onchip-Boot ROM. Boot ROM läser tillståndet för 14 konfigurationsstift för boot-läge som väljer vilka av de många externa RT1052-minnesgränssnitten som ska användas för programminne. Bland alternativen finns ett externt eMMC-kort, ett Micro SD-kort, ett konventionellt parallellt gränssnitt eller SPI XiP (i det här fallet Adestos ATXP032-CCUE-T).

Figur 3: NXP RT1052 Flashless-mikrostyrenhet har ett oktalt SPI XiP-gränssnitt som kan samverka enkelt med Adesto ATXP032-CCUE-T. Det oktala SPI XiP-gränssnittet är transparent för Arm-kärnan. (Bildkälla: DigiKey)

Figur 3: NXP RT1052 Flashless-mikrostyrenhet har ett oktalt SPI XiP-gränssnitt som kan samverka enkelt med Adesto ATXP032-CCUE-T. Det oktala SPI XiP-gränssnittet är transparent för Arm-kärnan. (Bildkälla: DigiKey)

RT1052-boot-alternativen omfattar även nedladdning av kod från USB OTG eller UART som ska köras från SRAM. Boot-lägesalternativ kan även anges vid tillverkning genom interna säkringar i RT1052 istället för att använda konfigurationsstift för boot-läge. När det oktala SPI XiP-gränssnittet aktiveras för programminneskärning av RT1052:s Boot ROM sker programkörningen omedelbart. Arm-kärnan kör sedan fast programvara från Adesto ATXP032-CCUE-T på samma sätt som från en extern parallell Flash-enhet eller intern Flash.

På grund av de snabba dataöverföringarna ska det oktala seriella Flashminnet sitta så nära som möjligt till mikrostyrenhetens oktala SPI XiP-port på PC-kortet. För att minska störningar bör inget av PC-spåren vara längre än 120 mm. Klocksignalen ska vara minst tre gånger bredden på PC-kortets spår från andra signaler för att undvika störningar. I/O [0:7] dubbelriktade datasignaler ska vara inom 10 mm från varandra för att undvika förskjutning.

Slutsats

IoT-slutpunkter har ökade minneskrav på grund av trender mot edge-databehandling och behovet av OTA-uppdateringar och associerade minnesskalbarhetsbehov. Vid någon tillfälle kan konstruktörer av dessa slutpunktsenheter upptäcka att Flashless-mikrostyrenhet kan vara ett tänkbart alternativ.

Framstegen för Flashless-mikrostyrenheter, höghastighetsgränssnitt och oktala SPI XiP Flash-chip ger utvecklare alternativet att skapa högpresterande kostnadseffektiva IoT-slutpunkter eller inbäddade system i stället för att använda traditionella Flash-baserade mikrostyrenhetsmetoder.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.