Grunder om frekvenssyntetisatorer med faslåsta slingor

Bidraget med av DigiKeys nordamerikanska redaktörer

2021-02-03

Stigande datahastigheter i snabba seriella kommunikationsbussar kräver systemklockor med högre frekvenser, större stabilitet, högre frekvensupplösning och högre signalrenhet. Direkta digitala syntetisatorer erbjuder dessa egenskaper, men bara vid frekvenser under 2 eller 3 GHz. En lösning krävs för frekvenser på upp till tiotals gigahertz.

Denna lösning börjar med PLL-baserade analoga frekvenssyntetisatorer som genererar klockfrekvenser upp till 30 GHz. Därefter använder Integer N-syntetisatorer (som multiplicerar referensfrekvensen med ett heltal) och Fraction N-syntetisatorer (som multiplicerar referensfrekvensen med bråktalsfaktorer) använder speciella tekniker som minimerar fasbrus och liknande signalföroreningar.

Denna artikel beskriver utformningen av både Integer N- och Fractional N-frekvenssyntetisatorer med hjälp av exempel från Analog Devices. Artikeln belyser också de innovationer som gör att dessa enheter kan användas för snabba seriella datalänkar såväl som för radar med varierande frekvens.

Integer N-syntetisatorer med faslåst slinga

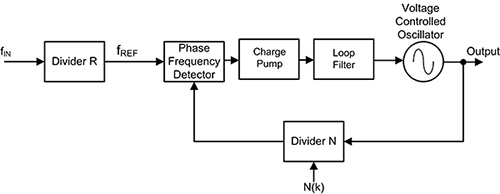

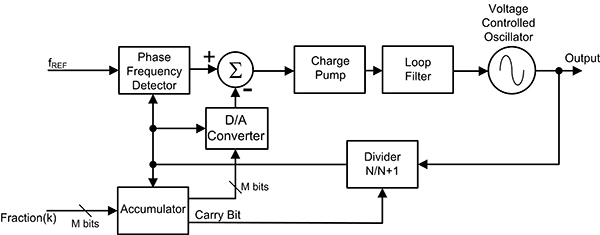

PLL-kretsar används för frekvens- och fasstyrning. De kan konfigureras som klockkällor, frekvensmultiplikatorer, demodulatorer, följargeneratorer eller klockåterställningskretsar. Var och en av dessa applikationer kräver olika egenskaper, men de använder alla samma grundläggande kretskoncept. Figur 1 visar ett blockschema över en grundläggande PLL konfigurerad som en frekvensmultiplikator.

Figur 1: Blockdiagram över en klassisk Integer N-frekvenssyntetisator med faslåsta slinga. (Bildkälla: DigiKey)

Figur 1: Blockdiagram över en klassisk Integer N-frekvenssyntetisator med faslåsta slinga. (Bildkälla: DigiKey)

Funktionen för denna krets är typisk för alla faslåsta slingor. Det är i grunden ett återkopplingsstyrsystem som styr fasen i en spänningsstyrd oscillator (VCO). Ingångssignalen matas till en förskalningsdelare, som delar ingångsfrekvensen med en faktor R. Utgången från förskalaren är referensfrekvensen, som bildar en ingång i en fasfrekvensdetektor (PFD).

Den andra PFD-ingången är en återkopplingssignal från utgången från en dela-med-N-räknare. Normalt, om PLL är låst, kommer båda signalerna att vara nästan desamma. Utgången från fasdetektorn är en spänning som står i proportion till fasdifferensen mellan de två ingångarna. Om slingan är upplåst, vilket händer vid start eller om det sker en stor momentan förskjutning av ingångsfrekvensen, används fasfrekvensdetektorn för att styra PLL-arbetsfrekvensen till önskad inställning. När denna frekvens uppnås, återgår PFD:n till fasdetektorläge och har en utsignal som är proportionell mot fasskillnaden mellan referensfrekvensen och återkopplingssignalen.

Fasfrekvensdetektorn driver en laddningspump som är en bipolär strömkälla. Detta betyder att den kan mata ut positiva och negativa strömpulser till slingfiltret i den faslåsta slingan.

Slingfiltret utjämnar fasfelsignalen och avgör också PLL:ns dynamiska egenskaper. Den filtrerade signalen reglerar VCO:n. Observera att utgången från VCO:n ligger på en frekvens som är N gånger den ingång som matas till frekvensreferensingången till fasfrekvensdetektorn och är N/R gånger frekvensingången. Denna utsignal skickas tillbaka till fasdetektorn via dela-med-N-räknaren.

Normalt sett utformas loopfiltret för att matcha egenskaperna som krävs av PLL-kretsen. Om PLL-kretsen ska registrera och följa en signal, måste bandbredden för loopfiltret vara större än om en fast inmatningsfrekvens förväntas. Frekvensområdet som den faslåsta slingan accepterar och kan låsa till kallas registreringsintervall. När den faslåsta slingan är låst och följer en signal, benämns frekvensintervallet - som den faslåsta slingan följer - följarintervall. Följarintervallet är vanligen större än registreringsintervallet. PLL-slingfiltret avgör också hur snabbt signalfrekvensen kan ändras och ändå behålla låsningen - dvs. den maximala förändringshastigheten. Ju smalare bandbredd slingfiltret har, desto smalare blir det uppnåbara fasfelet. Detta görs på bekostnad av långsammare respons och minskat registreringsintervall. PLL:er som används i klocktillämpningar arbetar primärt vid fasta frekvenser. I allmänhet bör bandbredden för slingfiltret vara mycket mindre än referensfrekvensen.

Eftersom PLL-utfrekvensen är en heltalsmultipel av referensfrekvensen, är dess frekvensupplösning lika med referensfrekvensen. För att få en finare frekvensupplösning krävs att referensfrekvensen minskas, vilket görs med räknaren R.

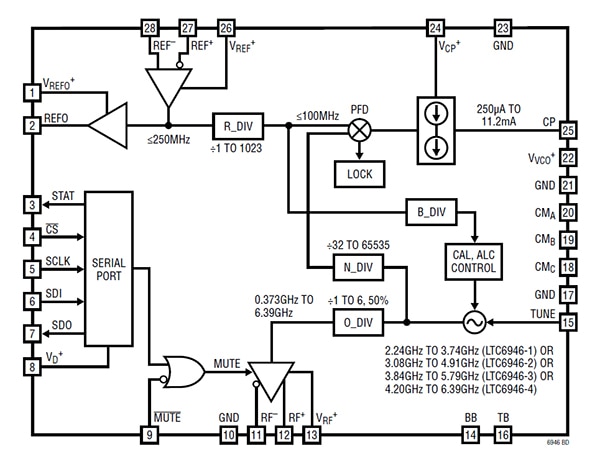

Ett kommersiellt exempel på en Integer N-frekvenssyntetisator är Analog Devices LTC6946IUFD-3 # PBF, en lågbrusig 0,64 till 5,790 GHz syntetisator med integrerad VCO och utmärkt störningsprestanda (figur 2). Den ingår i en familj med fyra syntetisatorkretsar, var och en med olika frekvensomomfång, som täcker ett totalt omfång på 0,373 till 6,390 GHz.

Figur 2: Blockdiagrammet för Analog Devices Integer N-frekvenssyntetisator LTC6946IUFD-3 # PBF med integrerad VCO. (Bildkälla: Analog Devices)

Figur 2: Blockdiagrammet för Analog Devices Integer N-frekvenssyntetisator LTC6946IUFD-3 # PBF med integrerad VCO. (Bildkälla: Analog Devices)

Denna syntetisator kräver ett externt slingfilter från användaren som kan optimeras för den specifika tillämpningen. Det finns en intern räknardelare före skalning med ett delningsområde från 1 till 1023. Delaren för slingan har ett intervall från 32 till 65535. Laddningspumpens ström kan ställas in från 250 mikroampere till 11,2 milliampere för att matcha kraven från slingfiltret.

Faslåsta Fractional N-slingsyntetisatorer

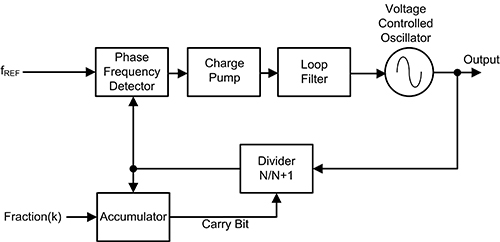

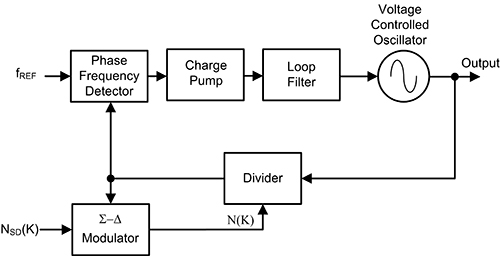

Frekvensupplösningen för PLL-syntetisatorn kan förbättras genom att reducera stegstorleken till mindre än helvärden - dvs. genom att göra bråktalssteg i slingdelaren (N). Detta uppnås genom att dynamiskt variera eller "darra" nedräkningsvärdet. Detta innebär att delarinställningen håller värdet N för ett fast antal cykler av PLL-utfrekvensen och periodiskt stegas till ett annat värde, såsom N + 1. Om exempelvis delningsinställningen är 4 för tre referensperioder och 5 för den fjärde referenscykeln, är den effektiva nedräkningen 4,25. Ett sätt att uppnå detta är att använda en ackumulator enligt figur 3.

Figur 3: Blockdiagrammet för en Fractional N-PLL-syntetisator som använder en ackumulator för att modulera delarvärdet. (Bildkälla: DigiKey)

Figur 3: Blockdiagrammet för en Fractional N-PLL-syntetisator som använder en ackumulator för att modulera delarvärdet. (Bildkälla: DigiKey)

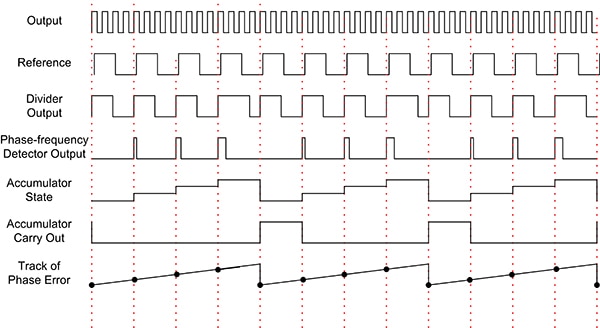

Ackumulatorn räknar utmatningspulserna från delaren, och varje M, där M är ackumulatorns modul, matar den ut en bärbit som ändrar delaringången. Figur 4 fortsätter exemplet med att ställa in en bråkdelsinställning på 4,25.

Figur 4: Tidsdiagram för en Fractional N-syntetisator med en ackumulator. (Bildkälla: DigiKey)

Figur 4: Tidsdiagram för en Fractional N-syntetisator med en ackumulator. (Bildkälla: DigiKey)

Ackumulatorn drivs av den delade utgången och räknarens modul - dvs. M - är 4. Var fjärde puls genererar den en bärutgång som ökar delningsantalet med 1. Ackumulatorn nollställs och börjar räkna igen. Ökningen i delarinställningen förskjuter utfrekvensen, vilket resulterar i ett ackumulerat fasförskjutningsfel. Följningen av fasfelet visar pulsvärdet som en funktion av tiden.

Den genomsnittliga delarinställningen är 4,25, men syntetisator-utgången är fasmodulerad, vilket resulterar i störtoner på utgången. Om man tittar på ackumulatortillståndet, är det uppenbart att det följer fasfelet. Detta kan användas för att ta bort moduleringen som visas i figur 5.

Figur 5: Användning av det D/A-omvandlade ackumulatortillståndet för att släcka ut fasmoduleringen till följd av Fractional N-darrningen. (Bildkälla: DigiKey)

Figur 5: Användning av det D/A-omvandlade ackumulatortillståndet för att släcka ut fasmoduleringen till följd av Fractional N-darrningen. (Bildkälla: DigiKey)

Ackumulatortillståndet omvandlas till ett analogt värde av en D/A-omvandlare och skalas och subtraheras från fasfrekvensdetektorutgången för att släcka ut fasmoduleringen till följd av Fractional N-darrningen. Detta måste göras med stor försiktighet. Om korrigeringssignalen inte exakt matchar fasfelet, kommer störfelstoner att uppstå på utgången.

Möt Sigma-Delta-modulatorn

Periodiciteten i ackumulatorn är orsaken till störutgångsdata från syntetisatorn. Om ackumulatorn bytr ut mot en Sigma-Delta-modulator kan digitala tekniker användas för att modulera delarvärdet på ett sätt som minimerar störsvar och brus. Detta utbyte visas i figur 6.

Figur 6: Att byta ackumulatorn mot en Sigma-Delta-modulator gör det möjligt att använda digitala tekniker för att variera delarvärdet för att reducera störsvaret. (Bildkälla: DigiKey)

Figur 6: Att byta ackumulatorn mot en Sigma-Delta-modulator gör det möjligt att använda digitala tekniker för att variera delarvärdet för att reducera störsvaret. (Bildkälla: DigiKey)

Det finns egentligen två vanliga digitala tekniker som används i Digma-Delta-moduleringstopologin. Den första handlar om att öka antalet N-delningsräkningar över ett bredare intervall av värden så att den genomsnittliga delningsfaktorn producerar det önskade bråktalsdelningsvärdet. Detta kommer att reducera de primära bråktalsstörningarna. Den ackumulatorbaserade syntetisatorn varierar antalet mellan två tillstånd. Detta är en första ordningens moduleringsmetod. En n-ordningens Sigma-Delta Fractional PLL modulerar N-räknaren mellan 2n olika värden. Till exempel kan en tredje ordningens modulator växla mellan åtta olika delningsvärden och en fjärde ordningens modulator kan växla mellan 16 olika delningsvärden.

Den andra digitala tekniken - även kallad darrning - innefattar randomisering av 2N-sekvensen så att den är pseudoslumpmässig. Samtidigt som den upprätthåller ett genomsnittligt bråktalsdelningsförhållande, omvandlar det bråktalsstörningsfelet till ett format, slumpmässigt brus på ett sådant sätt att det kan filtreras av PLL:n.

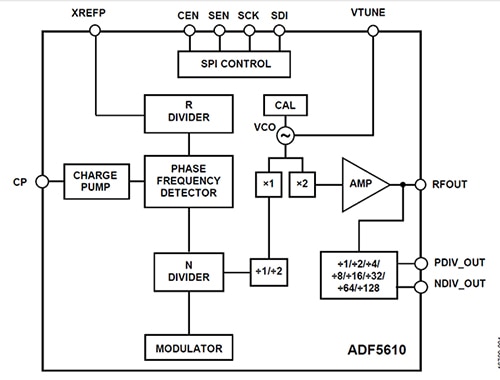

En kommersiell version av en Sigma-Delta-baserad Fractional N-syntetisator är Analog DevicesADF5610BCCZ, en lågbrusig 0,57 MHz till 14,6 GHz Fractional N-syntetisator med en integrerad VCO (Figur 7).

Figur 7: Ett blockschema för Analog Devices ADF5610BCCZ som stöder konfigurationer med både med Fractional N- och heltalssyntetisator. (Bildkälla: Analog Devices)

Figur 7: Ett blockschema för Analog Devices ADF5610BCCZ som stöder konfigurationer med både med Fractional N- och heltalssyntetisator. (Bildkälla: Analog Devices)

ADF5610 kräver en extern referensoscillator och slingfilter. Den har en integrerad VCO med en grundfrekvens på 3650 MHz till 7300 MHz. Dessa frekvenser fördubblas internt och dirigeras till RFOUT-pinnen. Det finns en differentialutgång som gör att den dubbla VCO-frekvensen kan delas med faktorerna 1, 2, 4, 8, 16, 32, 64 eller 128, vilket gör det möjligt att generera RF-utgångsfrekvenser så låga som 57 MHz.

ADF5610 använder en avancerad Sigma-Delta-modulator med en 24-bitars bråktalsmodul som uppnår exceptionellt låga störfelsnivåer. Som alla syntetisatorer som använder en Sigma-Delta-modulator, använder även denna enhet digitala signalbehandlingstekniker för att hitta det önskade genomsnittliga bråktalsdelningsförhållandet. Denna process, klockad med PFD-hastighet, producerar ett utgångsmodulationsbrus som kallas kvantiseringsbrus med högt passfrekvenssvar. Det externa lågpassfiltret används för att filtrera detta kvantiseringsbrus till en nivå under fasbruset hos VCO:n, vilket därmed förhindrar att bruset bidrar till systemets totala fasbrus.

ADF5610 innehåller också ett exakt frekvensläge för 0 Hz frekvensfel. Detta läge kan generera exakta frekvenser mellan intilliggande Integer N-gränssteg medan den fortfarande använder hela 24-bitars fasackumulatormodulen. Det uppnår exakta frekvenssteg med en hög jämförelseshastighet för fasdetekteringen, vilket gör att PLL:n kan bibehålla ett utmärkt fasbrus och störprestanda i detta läge.

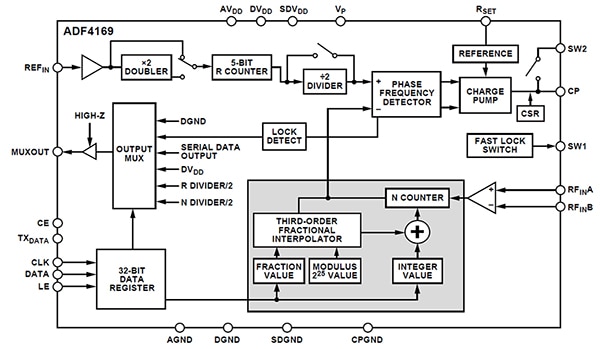

Analog Devices ADF4169CCPZ-RL7 är en annan PLL-syntetisator som kan konfigureras som antingen ett Integer N- eller en Fractional N-anordning. Den fungerar med en RF-bandbredd på upp till 13,5 GHz med modulering och vågformsgenerering. Den använder en extern referensfrekvensingång, VCO och slingfilter. Den har en tredje ordningens Sigma-Delta-modulator för Fractional N-syntes som kan inaktiveras, vilket gör att enheten kan köras i Integer N-läge (figur 8).

Figur 8: Analog Devices ADF4169CCPZ-RL7 använder en tredje ordningens Sigma-Delta-modulator. (Bildkälla: Analog Devices)

Figur 8: Analog Devices ADF4169CCPZ-RL7 använder en tredje ordningens Sigma-Delta-modulator. (Bildkälla: Analog Devices)

ADF4158WCCPZ-RL7-syntetisatorn är avsedd för användning i frekvensmodulerad kontinuerlig vågradar (FMCW). Den klarar olika typer av modulerade vågformer i frekvensdomänen, inklusive sågtand och triangulära ramper. Detta är en speciell funktion som är nödvändig i radartillämpningar.

Slutsats

Stigande datahastigheter i snabba seriella kommunikationsbussar kräver att konstruktörer letar bortom direkta digitala syntetisatorer - vilka fungerar bäst under 3 GHz - för systemklocklösningar. PLL-baserade frekvenssyntetisatorer som använder Integer N- och Fractional N-topologier ger stabila signaler med låg ljudnivå för högfrekvent klockning, seriell datakommunikation och radartillämpningar för frekvenser upp till 10-tals gigahertz.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.