Dra nytta av I3C för snabbare, enklare och mer flexibel kommunikation mellan integrerade kretsar

Bidraget med av DigiKeys nordamerikanska redaktörer

2024-12-17

Seriegränssnitt för kommunikation mellan integrerade kretsar (IC) domineras av I²C (Inter-Integrated Circuit) och SPI (Serial Peripheral Interface), som har varit tillgängliga sedan 1980-talet. Gränssnitten används ofta för att ansluta sensorer och integrerade kretsar med lägre hastighet till microcontrollers (MCU) för kommunikation mellan kretskort på korta avstånd. Men i takt med att de digitala systemen blir allt snabbare har gränssnitten, som är begränsade till typiska datahastigheter på 1 Mbit/s för I²C och 10 Mbit/s för SPI, blivit en begränsande faktor. Andra begränsningar, som t.ex. dedicerade ledare för avbrott eller val av krets, kräver ytterligare signalanslutningar, vilket ökar antalet trådar och komplexiteten i bussanslutningarna.

I3C-bussen (Improved Inter-Integrated Circuit) är avsedd att uppgradera kommunikationen mellan kretsar. Den ger högre datahastigheter, större flexibilitet och ett äkta tvåtrådsgränssnitt med IBI:er (in-band interrupts) istället för externa.

Artikeln beskriver egenskaperna hos I3C-gränssnittet och varför det kan vara en bra uppgradering från de seriella gränssnitten I²C och SPI. Typiska MCU:er, IC-switchar och sensorenheter kommer att användas för att visa dess tillämpning.

Inbyggda kommunikationsbussar

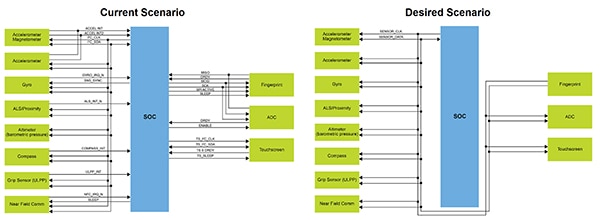

Inbyggda seriella kommunikationsbussar som I²C och SPI har använts i många år för kommunikation mellan kretskort. De används främst som kommunikationsbussar mellan sensorer och användargränssnitt och deras styrprocessorer. Antalet sensorer i typiska system har ökat från tio till tjugo i en telefon och betydligt fler i fordon. Samtidigt har kommunikationskraven blivit allt mer utmanande för konstruktörerna eftersom kraven ökar på högre hastighet, lägre strömförbrukning och färre ledare. Konstruktörer behöver uppfylla dessa krav och samtidigt behålla processorstyrningen via ledare för avbrott och aktivering (figur 1).

Figur 1: Kommunikation i inbyggda system bör stödja högre hastigheter, lägre effekt och ett minimalt antal trådar. (Bildkälla: NXP Semiconductor)

Figur 1: Kommunikation i inbyggda system bör stödja högre hastigheter, lägre effekt och ett minimalt antal trådar. (Bildkälla: NXP Semiconductor)

Med dagens teknik implementeras gränssnittet för sensorn och användarens styrenhet med hjälp av tvåtrådiga I²C- eller fyrtrådiga SPI-gränssnitt. Ledare för avbrott, aktivering och andra styrningar är separerade från ledarna för klocka och data, vilket medför fler ledare per gränssnitt.

Konstruktörer behöver en mer framåtblickande gränssnittsmetod som eliminerar dessa extra ledare från sammankopplingarna och hanterar funktionerna i kommunikationen med hjälp av endast klock- och dataledarna. Bussen måste dessutom kunna köras i högre hastigheter och med lägre effektförluster.

I3C-gränssnitt

I3C utvecklades av Mobile Industry Processor Interface (MIPI) Alliance för att uppfylla dessa krav. Gränssnittet är tillgängligt både som MIPI I3C för MIPI-medlemmar och som MIPI I3C Basic med reducerad funktionalitet för icke-medlemmar. Precis som de äldre gränssnitten I²C- och SPI är den förbättrade formen seriell och implementeras med två ledare för att minimera antalet stift och antalet signalvägar mellan komponenterna. De har en datahastighet på upp till 12,5 Mbit/s med en klockfrekvens på 12,5 MHz i SDR-läge (Single Data Rate). Den arbetar med lägre effektnivåer och använder en enkel men flexibel designarkitektur.

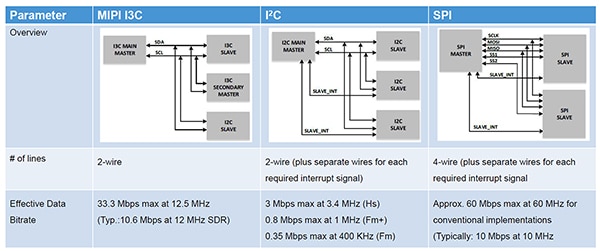

I3C-standarden har begränsad bakåtkompatibilitet med I²C-systemet, vilket gör att befintliga I²C-enheter kan anslutas till I3C-bussen, samtidigt som bussen kan växla till högre datahastigheter för kommunikation mellan kompatibla I3C-enheter. En jämförelse av systemkonfigurationerna visas i figur 2.

Figur 2: En jämförelse mellan grundkonfigurationerna för gränssnitten I3C, I²C och SPI visar att I3C är snabbare och har enklare kabeldragning. (Bildkälla: NXP Semiconductors)

Figur 2: En jämförelse mellan grundkonfigurationerna för gränssnitten I3C, I²C och SPI visar att I3C är snabbare och har enklare kabeldragning. (Bildkälla: NXP Semiconductors)

Det fyrtrådiga SPI-gränssnittet kan arbeta snabbare och har stöd för full duplex-kommunikation. I²C kommunicerar med halv duplex över en tvåtrådig buss som består av ledare för klocka (SCL) och data (SDA). Båda kräver extra ledare för att stödja interrupt och andra styrfunktioner som val av krets. I3C minskar antalet ledare som används i gränssnittet till två och eliminerar de separata ledarna för avbrott, aktivering och val av krets som används i I²C och SPI. Denna minskning av antalet ledare är en betydande fördel i ett system som kräver tio till tjugo individuella sensorer kopplade till processorn, var och en med flera sekundära kablar. Avbrott och andra ledare för styrning ersätts av IBI:er. Med den här metoden lägger en avsedd sensor eller enhet in sin adress i I3C-bussens adresshuvud för att meddela processorn om ett interrupt.

Skillnaden i klockfrekvens mellan I²C och I3C är betydande. I²C klockas i allmänhet med 100 kHz, 400 kHz eller 1 MHz, medan I3C kan klockas med 12,5 MHz. Tidigare användes SPI för klockfrekvenser högre än 1 MHz. Konstruktionsvalet stod mellan klockfrekvensen och antalet ledare. I3C har ändrat på detta genom att erbjuda högre klock- och datahastigheter med hjälp av en äkta tvåtråds-topologi.

Utgångar med push-pull, som kan växla snabbare än drivkretsar med open-drain eller open collector, är en viktig bidragande orsak till den ökade klockfrekvensen hos I3C. För att bibehålla kompatibiliteten med I²C-enheter kan I3C växla mellan drivkretsar med open-drain och push-pull beroende på bussens status. Konstruktioner med open-drain eller open collector används vid initial adressering eller förhandling, där både I²C- och I3C-enheter kan vara på linjen samtidigt. I3C använder push-pull när kommunikationen är enkelriktad och det inte finns någon risk för att en I²C-enhet kommunicerar samtidigt.

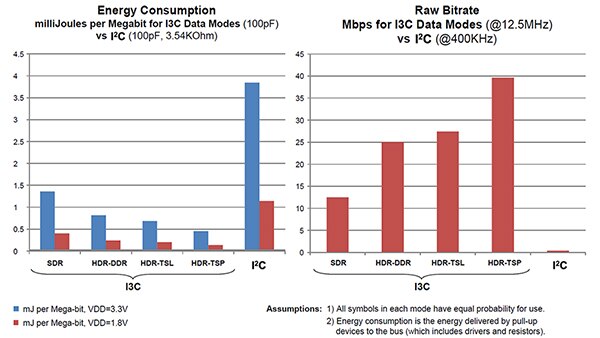

Förutom standard SDR stöder I3C flera valfria HDR-lägen (High Data Rate). Dessa HDR-lägen arbetar med samma klockfrekvens men sänder med en högre datatäthet. Det första av HDR-lägena är HDR-DDR (HDR Double Data Rate), där data klockas på båda flankerna av klocksignalen, vilket ger nästan dubbelt så hög datahastighet. Med en klockfrekvens på 12,5 MHz uppnår DDR-läget en effektiv datahastighet på 20 Mbit/s.

HDR ternary-symboler finns i dubbla versioner: HDR ternary symbol, pure (HDR-TSP) endast för I3C-enheter och HDR ternary symbol, legacy (HDR-TSL) för bussar som innehåller enheter med både I²C och I3C. Ternary symbol-lägen uppnår tre databitar per klockning med hjälp av tre-bitars (ternary) symboler som kodas på SCL- och SDA-ledarna.

Läget för HDR-BT (HDR Bulk Transport) ger högsta möjliga datatrafik genom att stödja kommunikation via fyrdubbla, dubbla eller enkla SDA-dataledare. Det medför åtta, fyra eller två gånger högre prestanda för en enda datahastighet vid samma klockfrekvens.

Ökningarna av dataöverföringshastigheten gör att enheterna kan vara påslagna under en kortare period, vilket minskar bussens effektcykel. Detta minskar strömförbrukningen jämfört med I²C (figur 3). Bytet från drivkretsar med open collector med externa pull-up-resistorer till drivkretsar med push-pull minskar strömförbrukningen ytterligare, eftersom pull-up-resistorerna kräver en betydande ström för att fungera.

Figur 3: I3C ger förbättringar i datahastighet och strömförbrukning jämfört med I²C. (Bildkälla: NXP Semiconductors)

Figur 3: I3C ger förbättringar i datahastighet och strömförbrukning jämfört med I²C. (Bildkälla: NXP Semiconductors)

Adressering

I²C använder statiska adresser med antingen 7 eller 10 bitars längd för respektive bussenhet. Detta har ändrats i I3C till 7-bitars dynamisk adressering, där bussens master-enhet ställer in enhetsadressen vid dynamisk adresstilldelning (DAA) och lagrar den i ett enhetsregister. Statisk adressering, som i fallet med en kringutrustning för I²C, kan fortfarande användas i I3C.

Tack vare dynamisk adressering kan enhetsadresser ändras i efterhand. Detta stöder sammankoppling under drift, vilket innebär att en ny enhet kan läggas till på bussen medan den är i drift. Den nya enheten, som är ansluten till I3C-bussen, signalerar sin närvaro till I3C-bussens master-enhet genom att skicka en begäran om sammankoppling under drift. Master-enheten bekräftar begäran och tilldelar en adress för att lägga till enheten på bussen.

IBI:er

I3C är en äkta tvåtrådsbuss som använder IBI:er i stället för dedicerade avbrottslinjer som I²C. IBI:er är när en målenhet signalerar sin tillgänglighet till master-enheten genom att sänka SDA-ledaren. Master-enheten startar då SCL-ledarens klocka och målenheten skickar sin adress till I3C-bussen för att meddela styrenheten om ett avbrott.

Vanliga styrkoder

Vanliga styrkoder (Common Command Codes eller CCC) är standardiserade kommandon som styrenheten kan skicka som en allmän sändning till alla I3C-enheter samtidigt eller till en specifik målenhet. Dessa kommandon är avsedda för saker som rör busshantering. Formatet för CCC-protokollet inleds med broadcast-adressen för I3C-bussen, som känns igen av alla I3C-enheter på bussen. Eventuella I²C-enheter på bussen kommer inte att bekräfta begäran eftersom det är en reserverad I²C-adress.

Respektive kommando innehåller ett 8-bitars ID-fält för beskrivning och kan följas av en nyttolast med ett kommando. Ett kommando som skickas till en specifik enhet skickar enhetens adress i den första byten i nyttolasten. Det finns över fyrtio CCC-kommandon, inklusive:

- Ange dynamisk adresstilldelning (ENTDAA)

- Ange ny dynamisk adresstilldelning (SETNEWDA)

- Aktivera händelser (ENEC)/Inaktivera händelser (DISEC)

- Återställ dynamisk adresstilldelning (RSTDAA)

- Gå till läge för hög datahastighet (ENTHDRx)

- Hämta register för enhetsegenskaper (GETDCR)

Leverantörer har tillgång till ett särskilt antal CCC-ID:n för att kunna implementera sina egna kommandon.

Detektering och återställning av fel

Till skillnad från I²C innehåller I3C villkor för detektering och återställning av fel. Sex metoder för fel och återställning för målenheter är obligatoriska, och ytterligare en är valfri. Ytterligare metoder för fel och återställning finns också tillgängliga specifikt för fel på huvudenhetens sida.

Komponenter som stöds av I3C

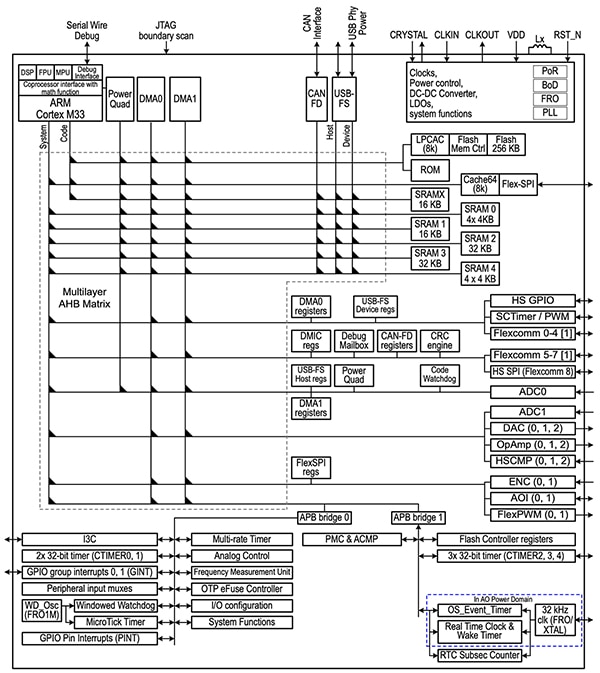

Som visas i figur 2 (vänster) består ett grundläggande I3C-nätverk av minst en huvudstyrenhet (master) och ett eller flera I3C-mål eller slavar. Master-enheten kan vara en MCU, t.ex. LPC5534JHI48-00MP från NXP Semiconductor (bild 4). Det är en 32-bitars Arm® Cortex®-M33 MCU med 128 kilobyte (Kbytes) SRAM och 256 Kbytes Flash. Dess Flexcomm-gränssnitt stöder åtta olika seriella gränssnitt, inklusive I3C.

Bild 4: MCU:n LPC5534JHI48/00MP har ett I3C-gränssnitt och sju andra seriella gränssnitt. (Bildkälla: NXP Semiconductor)

Bild 4: MCU:n LPC5534JHI48/00MP har ett I3C-gränssnitt och sju andra seriella gränssnitt. (Bildkälla: NXP Semiconductor)

I3C-bussen tillåter tillägg av sekundära master-enheter som introduceras till bussen som slavar. I3C kan ha flera master-enheter, men bara en kan vara styrenhet. När den sekundära master-enheten har registrerat sig kan den begära status från den nuvarande master-enheten, och om den nuvarande master-enheten godkänner detta överförs styrningen till den sekundära master-enhet som begär det.

En typisk sensor för I3C är P3T2030CUKAZ från NXP. Denna temperaturgivare omvandlar temperaturer från -40 °C till +125 °C till ett 12-bitars digitalt värde med en noggrannhet på ±2 °C. Den innehåller både gränssnittet I²C och I3C med SDR-läge.

En mer sofistikerad sensor är det treaxliga MEMS-gyroskopet och accelerometern ICM-42605 från TDK InvenSense. Som hastighetsgyro mäter den snurrhastigheter från ±15,2 till ±2000°/s. Som accelerometer har den ett mätområde på ±2 till ±15 g. Den känner av rörelse, lutning, tryck eller steg (stegräknare). Som I3C-sensor arbetar den med 12,5 MHz i SDR-läge och 25 MHz i DDR-läge.

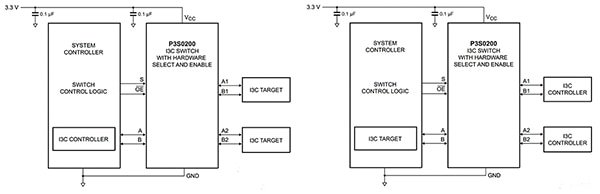

Integrerade kretsar som I3C-switchen P3S0200GMX från NXP kan omkonfigurera I3C-bussen genom att dirigera I3C-bussignaler mellan en styrenhet för I3C och flera uppsättningar målenheter, eller mellan en enda målenhet och flera I3C-styrenheter enligt vad som bestäms av en extern MCU (figur 5).

Figur 5: I3C-switchen P3S0200GMX kan användas för att konfigurera om en I3C-buss genom att dirigera I3C-bussens signaler mellan en I3C-styrenhet och flera uppsättningar målenheter, eller mellan en enda målenhet och flera I3C-styrenheter. (Bildkälla: NXP Semiconductors)

Figur 5: I3C-switchen P3S0200GMX kan användas för att konfigurera om en I3C-buss genom att dirigera I3C-bussens signaler mellan en I3C-styrenhet och flera uppsättningar målenheter, eller mellan en enda målenhet och flera I3C-styrenheter. (Bildkälla: NXP Semiconductors)

Det kan vara nödvändigt att växla mellan två mål om båda målen har samma adress och inte kan vara placerade på samma buss. Alternativt kan ett enda mål behöva delas mellan två processer, vilket kräver en omkoppling mellan de två I3C-styrenheterna.

Sammanfattning

I3C är ett seriellt gränssnitt som förbättrar I²C-bussen genom att öka dess datahastighet, minska antalet trådar och öka flexibiliteten i styrningen av bussen. Det är en förbättring som utökar användbarheten för äldre I²C- och SPI-gränssnitt.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.