Utvärdera och använda nollfördröjningsbuffertar för skyddad tidtagning i synkrona digitala system

Bidraget med av DigiKeys nordamerikanska redaktörer

2019-07-18

I takt med att digitala system får allt högre prestanda måste konstruktörer blir alltmer noggranna när de utformar kretsar för generering och distribution av klockan för att undvika att det uppstår differenser eller osäkerheter i tidtagningen. Sådana problem kan orsaka nedgradering av systemprestanda, minska tidtagningsmarginalerna eller leda till funktionsfel. För att undvika problem med förvrängning i tidtagningen kan konstruktörerna använda nollfördröjningsbuffertar.

Synkrona digitala system använder vanligen en gemensam klocka för att se till att åtgärderna utförs i rätt följd. Denna klocka måste distribueras till alla element i sekvensen för att systemet ska arbeta i önskad hastighet, och ofta regleras detta med en stängd loop för att reducera förvrängningen i tidtagningen. Nollfördröjningsbuffertar använder faslåsta loopar (PLL) för att säkerställa att de buffrade klockutgångarna justeras i förhållande till referensklockans indata, vilket gör att tidtagningen blir nära nog perfekt i klockan.

I den här artikeln beskrivs nollfördröjningsbuffertar, och den förklarar även hur de fungerar med hjälp av exempellösningar från Cypress Semiconductor, Integrated Device Technology Inc. (IDT) och ON Semiconductor. Den beskriver även styrning av klockförvrängning. I artikeln undersöks även testmetoder för att säkerställa att enheterna är stabila.

Klockförvrängning

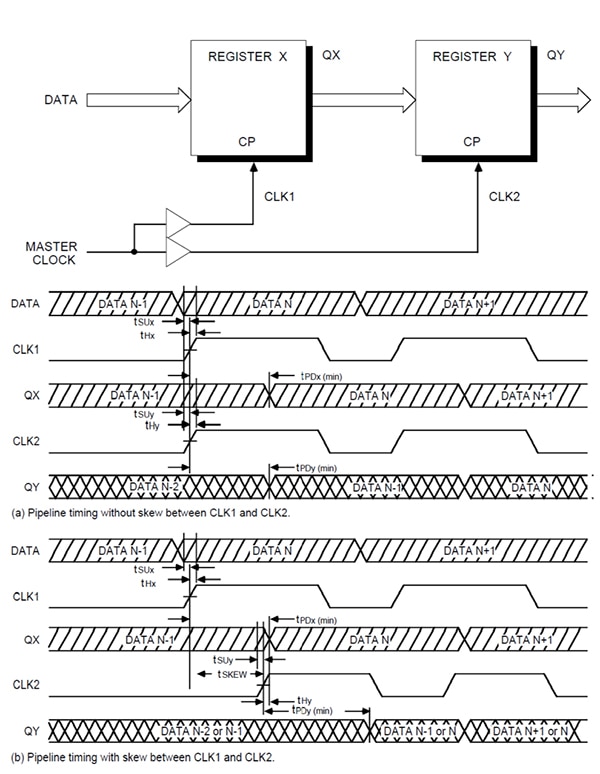

I synkrona digitala system kan klockorna visa olika tider i olika delar av kretsen och därmed orsaka klockförvrängning. Klockförvrängning kan reducera tidtagningsmarginalerna och orsaka systemfel (figur 1).

Figur 1: Ett enkelt exempel på hur fördröjning i klocktiden kan påverka åtgärder i register i pipeline. En klocka med förvrängning kan bryta mot installations- och/eller uppställningskrav och ge upphov till ett obestämt tillstånd för utgången. (Bildkälla: IDT)

Figur 1: Ett enkelt exempel på hur fördröjning i klocktiden kan påverka åtgärder i register i pipeline. En klocka med förvrängning kan bryta mot installations- och/eller uppställningskrav och ge upphov till ett obestämt tillstånd för utgången. (Bildkälla: IDT)

Vi utgår från ett enkelt synkront system bestående av två register. Data förs genom registren i pipeline så att utmatningen för register X, QX, blir inmatningen till register Y. Klockorna matas till registren via fristående buffertar och betecknas CLK1 och CLK2. Om det inte finns någon förvrängning mellan klockorna som visas i diagram (a), klockas datatillstånd N, enligt registrets installations- (tSUx) och (tHx) tidskrav, till register X-utgången, QX, vid den första klockkanten efter registrets propageringsfördröjning. Samma klockkant på CLK2 gör att det tidigare tillståndet för QX, N-1, läses av av registret och visas vid utgången QY efter registrets propageringsfördröjning.

Om det finns en tidsförvrängning mellan CLK1 och CLK2, som visas i diagram (b), kan tillståndet för QX fortfarande pågå när CLK2 inträder. Inmatningen till register Y kanske inte uppfyller registrets installations- eller uppställningstidkrav, och utgången kan bli obestämd vilket skapar ett fel.

För att säkerställa minimal klockförvrängning kan konstruktörer matcha längden på de tryckta kretsspåren, välja buffertar och andra klockkomponenter med liknande propageringsfördröjningar, samt balansera lasten på flera klockkällor. Dessa tekniker kan vara till hjälp, men nollfördröjningsbuffertar krävs vanligen för att få en bra kontroll över klockförvrängning.

Styra klockförvrängning

Klockförvrängning kan ha många källor. Den mest uppenbara är när klocksignaler leds över tryckta kretskopplingar med varierande längder. Andra källor kan vara att klockorna passerar genom olika aktiva enheter med skilda propageringsfördröjningar, klockbuffertar med olika last eller temperaturskillnader i buffertarna. Vissa av dessa effekter kan visserligen regleras, men konstruktörer använder ofta aktiva enheter för att omsynkronisera klockor till en referensklocka med hjälp av PLL:er.

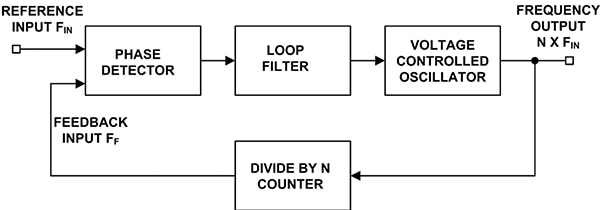

PLL-kretsar används för frekvens- och fasstyrning. De kan konfigureras som frekvensmultiplicerare, demodulatorer, spårgeneratorer eller klockåterställningskretsar. För var och en av dessa tillämpningar krävs olika egenskaper, men samtliga använder det kretskoncept som visas i figur 2 som bas.

Figur 2: Blockdiagram av en PLL som konfigurerats som frekvensmultiplicerare. I grunden är detta ett feedbackstyrsystem som reglerar fasen för en spänningsstyrd oscillator (VCO). (Bildkälla: DigiKey)

Figur 2: Blockdiagram av en PLL som konfigurerats som frekvensmultiplicerare. I grunden är detta ett feedbackstyrsystem som reglerar fasen för en spänningsstyrd oscillator (VCO). (Bildkälla: DigiKey)

Figur 2 visar ett blockdiagram av en grundläggande PLL som konfigurerats som frekvensmultiplicerare. Den här kretsen fungerar på ett sätt som är typiskt för alla PLL:er. I grunden är detta ett feedbackstyrsystem som reglerar fasen för en VCO. Insignalen tillämpas på en ingång i en fasdetektor. Den andra ingången är en feedbacksignal från utmatningen från en Divide-by-N-räknare. Normalt sett är frekvenserna för de båda signalerna nästan desamma.

Utgången från fasdetektorn är en spänning som står i proportion till fasdifferensen mellan de två ingångarna. Denna signal tillämpas på loopfiltret. Det är loopfiltret som avgör de dynamiska egenskaperna för PLL-kretsen. Den filtrerade signalen reglerar VCO:n. Notera att utmatningen från VCO:n har en frekvens som är N gånger den inmatning som leds till frekvensreferensingången (FIN). Denna utsignal skickas tillbaka till fasdetektorn via dela-med-N-räknaren.

Normalt sett utformas loopfiltret för att matcha egenskaperna som krävs av PLL-kretsen. Om PLL-kretsen ska registrera och följa en signal, måste bandbredden för loopfiltret vara större än om en fast inmatningsfrekvens förväntas. Frekvensomfånget som PLL-kretsen kommer att hantera och låsas vid kallas infångningsomfång. När PLL-kretsen har låsts och spårar en signal kallas omfånget med frekvenser som den kommer att följa spårningsomfånget. Följarintervallet är vanligen större än registreringsintervallet. PLL-kretsens loopfilter avgör även hur snabbt signalfrekvensen kan ändra sig och ändå förbli låst. Detta är den maximala ändringshastigheten. Ju smalare bandbredd slingfiltret har, desto smalare blir det uppnåbara fasfelet. Detta görs på bekostnad av långsammare respons och minskat registreringsintervall. PLL:er som används i klocktillämpningar arbetar primärt vid fasta frekvenser.

Nollfördröjningsbuffertar

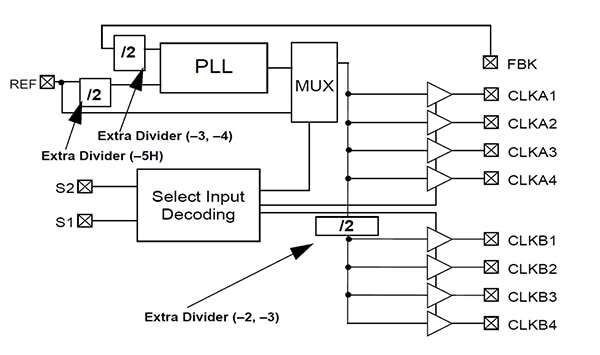

En nollfördröjningsbuffert är en enhet som kan buffra en klocksignal och skapa multipla klockutmatningar från en enskild referensklockeingång. De multipla buffrade klockutmatningarna har liten eller ingen fördröjning i förhållande till referensklockingången och en låg förvrängning mellan utgångarna. Det förenklade blockdiagrammet över nollfördröjningsbufferten Cypress Semiconductor CY2308SXC-3T visas i figur 3.

Figur 3: Nollfördröjningsbufferten CY2308SXC-3T med åtta utgångar använder en PLL för att synkronisera alla utgångar till en tidsförvrängning nära noll. (Bildkälla: Cypress Semiconductor)

Figur 3: Nollfördröjningsbufferten CY2308SXC-3T med åtta utgångar använder en PLL för att synkronisera alla utgångar till en tidsförvrängning nära noll. (Bildkälla: Cypress Semiconductor)

En nollfördröjningsbuffert byggs med en intern PLL som accepterar en referensingång (REF) och en feedbackingång (FBK) som inmatningar till sin fasdetektor. Feedbackingången drivs från den utgång som användaren väljer. Den interna fasdetektorn i PLL-kretsen justerar utgångsfasen för VCO:n så att dess två ingångar inte har någon fas- eller frekvensdifferens. En av de buffrade klockutmatningarna och dess last väljs som feedbacksignal till PLL-kretsen via fasdetektorn. Oavsett vilka lastförändringar som sker vid den utgången, kommer PLL-kretsen att dynamiskt kompensera för dessa lastförändringar i utmatningen, vilket ger noll fördröjning från ingången till utgången som driver feedbacksignalen, oavsett vilken utgångslast som gäller.

CY2308-familjen har två fält med fyra utgångar, vilka arbetar över ett frekvensomfång från 10 till 133 megahertz (MHz). Tidsförvrängningen från ingång till utgång är mindre än 250 picosekunder (ps) och klockförvrängningen mellan utgångarna är mindre än 200 ps. Tidsförvrängningen från ingång till utgång är justerbar genom att lastkapacitansen på utgången som används för feedbackinmatning kan ändras.

Produktfamiljen erbjuder ett flertal konfigurationer med Divide-by-2-delare. Den valda komponenten är ”-3”-varianten som har två sådana delare vilket visas i blockdiagrammet. Denna konfiguration gör att användaren kan få utmatningar på två eller fyra gånger referensklockans ingångsfrekvens.

Den nollfördröjningsbuffert som används mest är konfigurerad med fem utgångar och är tillgänglig från flera olika tillverkare. Cypress Semiconductor CY2305SXI-1HT, IDT 2305-1DCGI8 och ON Semiconductor NB2305AI1HDR2G är enheter som sinsemellan är väldigt lika. Samtliga har fem buffrade klockutgångar, en CLKOUT-port, samt ett fyrdelat fält med klockutgångar. Till skillnad från på CY2308 är PLL-kretsens feedbackpunkt fast på den enstaka CLKOUT-signalen.

Dynamiken i nollfördröjningsbuffertar

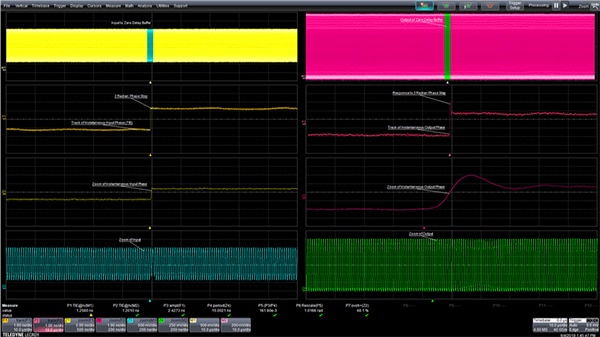

PLL-kretsarna i nollfördröjningsbuffertarna är i grunden feedbackstyrsystem. Dynamiken styrs av PLL-kretsens loopfilter. I likhet med andra styrsystem är det viktigt att utvärdera feedbackloopens dynamik som svar på en transient-inspänning. Ett sätt att göra detta är att tillämpa en inspänning med en stegförändring för att utvärdera stegets svar (figur 4).

Figur 4: Utvärdera stegsvaret för nollfördröjningsbufferten CY2305 med användning av ett fassteg med 1-radian vid 66,67 MHz. Rutnätet ovan till vänster visar insignalen och rutnätet ovan till höger motsvarar utmatningen. (Bildkälla: DigiKey)

Figur 4: Utvärdera stegsvaret för nollfördröjningsbufferten CY2305 med användning av ett fassteg med 1-radian vid 66,67 MHz. Rutnätet ovan till vänster visar insignalen och rutnätet ovan till höger motsvarar utmatningen. (Bildkälla: DigiKey)

Insignalen är 66,67 MHz sinus med ett steg på 1-radian i mitten av det inhämtade signalfönstret. Denna vågform genererades av en arbiträr vågformsgenerator (AWG). Såväl ingång som utgång på nollfördröjningsbufferten CY2305 inhämtades med hjälp av ett oscilloskop och en tidsbasinställning på 10 mikrosekunder (µs) per del.

Rutnätet ovan till vänster i figur 4 är insignalen, och rutnätet ovan till höger är utmatningen. Tidsintervallfelet (TIE) är tidsskillnaden mellan den uppmätta klockkanten till dess ideala position, och detta mäts för varje vågform. Detta utgör i allt väsentligt den momentana fasen i den signal som refereras till i en fast klockfrekvens, i det här fallet 66,67 MHz. Värdet för TIE för varje klockcykel både för ingång och utgång distribueras som en vågform som kallas ett TIE-spår. Spåret för ingången är det andra rutnätet sett uppifrån till vänster. Här visas steget i fasen med en amplitud på 2,4 nanosekunder (ns). Detta värde motsvarar en fasförskjutning på 1 radion för klockfrekvensen 66,67 MHz.

Det andra spåret ovanifrån till höger är TIE-spåret för utgången. Spåret för utgången visar en del översvängning och stannar på ett nytt medelvärde för att matcha den ändrade ingången. Det tredje spåret ovanifrån visar ett horisontellt expanderat zoomspår för ingången till vänster och till höger för utgången. Detaljerna för ingångssteget visar en ren övergång.

Zoomningen på utgången visar en del översvängning och ställer sedan snabbt in sig på det nya medelvärdet efter ungefär en cykel som varar cirka 500 ns. Detta är ett bra stegsvar för ett så stort fassteg. Den ställer snabbt in sig, och det finns inga tecken på ett ostabilt oscillatorsvar.

De två nedersta spåren visar horisontellt expanderade vyer över ingången (vänster) och utgången (höger). Det stora fassteget syns tydligt vid ingången, men det långsamma utgångssvaret syns mindre tydligt i denna tidsskala.

Sammanfattning

Konstruktörer som utformar högpresterande digitala system måste även fortsättningsvis vara mycket noggranna vid konstruktion av kretsar för generering och distribution av klockan för att undvika differenser eller osäkerhet vid tidtagning. Sådana problem kan orsaka nedgradering av systemprestanda, minska tidtagningsmarginalerna eller leda till funktionsfel.

Som beskrivits är nollfördröjningsbuffertar ett bra verktyg för aktiv kontroll vid propagering av multipla klocksignaler och för att upprätthålla synkroniseringen med signalen från en huvudklocka. Spårningen fungerar utmärkt även vid betydande lastförändringar i den avkända utgången. Konstruktörer måste dock som visas noga utvärdera dynamiken för feedbackloopen i nollfördröjningsbufferten och säkerställa att den uppfyller kraven för tillämpningen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.