Förstå och minimera effekterna av jitter i höghastighetslänkar

Bidraget med av DigiKeys nordamerikanska redaktörer

2023-12-21

Klockoscillatorer tillhandahåller den tidsmässiga styrfrekvensen genom att hålla systemkomponenterna i takt. När systemhastigheterna ökar till hundratals megahertz (MHz) och högre, måste klockorna bli snabbare och ha mycket lågt jitter, vanligtvis under 100 femtosekunder (fs), för att bibehålla systemets prestanda. De måste också bibehålla sina specifikationer för lågt jitter över tid, trots variationer i temperatur och spänning.

En del jitter orsakas av brus och distorsion i signalvägen, och det kan minskas något med hjälp av tekniker för omklockning och synkronisering. Jitter genereras dock även av klockkällan, som vanligtvis är en oscillator. Det beror på olika fysiska fenomen, som t.ex. termiska störningar, processfel, störningar i strömförsörjningen, andra externa störningar som tar sig in i klockoscillatorn, materialpåfrestningar och många andra subtila faktorer. Oavsett källan är det upp till konstruktören att göra allt för att minimera det inbyggda jittret i klockan, eftersom bristerna inte är reversibla.

Artikeln diskuterar jitter ur olika perspektiv. Därefter presenteras olika klockoscillatorer från Abracon LLC och den visar hur jitter kan minimeras genom att matcha klockoscillatorns prestanda till tillämpningen.

Grundkunskaper om jitter

Klockjitter är avvikelsen hos en klockas flank från dess perfekt position i tid. Detta jitter påverkar precisionen och noggrannheten i överföringen av de datasignaler som klocksignalen styr, vilket medför att signal-brusförhållandet (SNR) försämras i mottagarens avkodnings-/demoduleringskrets eller andra systemkretsar. Detta leder till en högre bitfelsfrekvens (BER), fler återsändningar och minskad effektiv datagenomströmning.

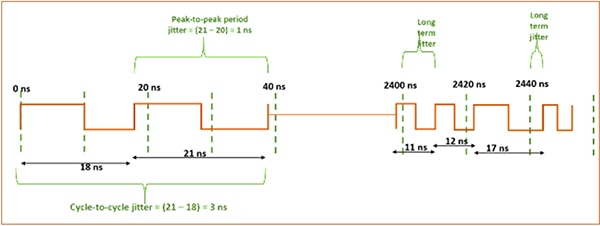

Eftersom klockjitter är så kritiskt analyseras det ofta i system som skickar en signal från en sändande källa till en mottagare via kablar, kontakter eller kretskort. Beroende på tillämpning kan det karakteriseras på många olika sätt, t.ex. cykel-till-cykel, periodiskt och långtidsjitter (figur 1).

Figur 1: Termen "jitter" omfattar många tidsvariationer, inklusive jitter från cykel till cykel, periodiskt jitter och långtidsjitter. (Bildkälla: VLSI Universe)

Figur 1: Termen "jitter" omfattar många tidsvariationer, inklusive jitter från cykel till cykel, periodiskt jitter och långtidsjitter. (Bildkälla: VLSI Universe)

- Jitter från cykel till cykel innebär en förändring av klockperioden i två på varandra följande cykler och är inte relaterat till frekvensvariationer över tiden.

- Periodiskt jitter är avvikelsen för en klockperiod i förhållande till dess genomsnittliga period. Det är skillnaden mellan den perfekta och den faktiska klockperioden, och kan anges antingen som periodiskt jitter i RMS (kvadratiskt medelvärde) eller periodiskt jitter med topp till topp.

- Långtidsjitter är avvikelsen från den perfekta positionen för klockans flank under en en längre tidsperiod. Det liknar i en viss mån avvikelse.

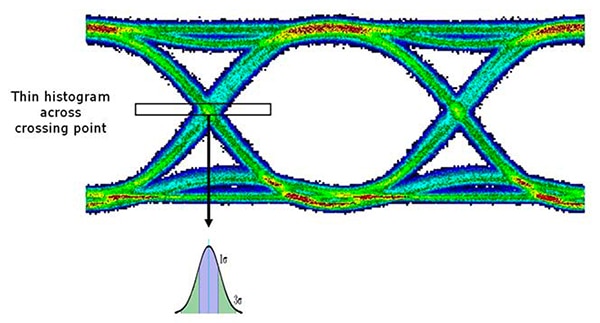

Jitter kan störa den timing som används av andra delfunktioner, komponenter eller system som används för att uppnå dataåterställning med låg BER, eller av komponenter som minneselement eller processorer i ett synkront system. Det är synligt i ögondiagrammet i figur 2 som en breddning av skärningspunkten för i timingen av bits.

Figur 2: I ett ögondiagram ses jitter som en breddning av den viktiga skärningspunkten för timing i dataströmmen. (Bildkälla: Kevin K. Gifford/Univ. Colorado)

Figur 2: I ett ögondiagram ses jitter som en breddning av den viktiga skärningspunkten för timing i dataströmmen. (Bildkälla: Kevin K. Gifford/Univ. Colorado)

För seriella datalänkar måste kretsarna på mottagarsidan försöka återskapa sin egen klocka för optimal avkodning av dataströmmen. För att göra detta måste den synkronisera och låsa på källklockan, ofta med hjälp av en faslåsningslinga (PLL). Jitter påverkar systemets förmåga att göra detta exakt, vilket äventyrar dess förmåga att återskapa data med en låg BER.

Observera att jitter kan mätas i både tids- och frekvensdomänen; båda är lika giltiga perspektiv på samma fenomen. Fasstörningar är en frekvensdominerad bild av störningsspektrumet kring oscillatorsignalen, medan jitter är ett tidsdominerat mått på oscillatorperiodens tidsnoggrannhet.

Mätningar av jitter kan uttryckas på flera sätt. Den anges vanligen med tidsenheter som "jitter per 10 pikosekunder" (ps). Fasjitter med RMS (kvadratiskt medelvärde) är en tidsdomänparameter som härleds från mätningen av fasstörningar (frekvensdomän). Jitter kallas ibland även för fasjitter, vilket kan vara förvirrande, men det är fortfarande en jitterparameter i tidsdomänen.

När länkarnas driftfrekvenser och deras klockor ökar från några tiotals till hundratals MHz och högre, minskar den tillåtna jittern på klockkällan till cirka 100 fs eller mindre. Dessa frekvenser gäller för optiska moduler, molnbaserad databehandling, nätverk och Ethernet med hög hastighet, som alla är funktioner och tillämpningar som kräver en bärfrekvens på mellan 100 och 212/215 MHz och datahastigheter på upp till 400 Gbit/s).

Hantering av kristallen

Det vanligaste sättet att skapa en stabil, jämn och exakt klocksignal är att använda en oscillator med kvartskristall. En tillhörande oscillatorkrets stödjer kristallen. Det finns många sådana kretsfamiljer, var och en med olika kompromisser. Kristaller har använts för det här ändamålet sedan 1930-talet för trådlös radiokommunikation i de medelfrekventa (300 kilohertz (kHz) till 3 MHz) och högfrekventa (3 till 30 MHz) RF-banden.

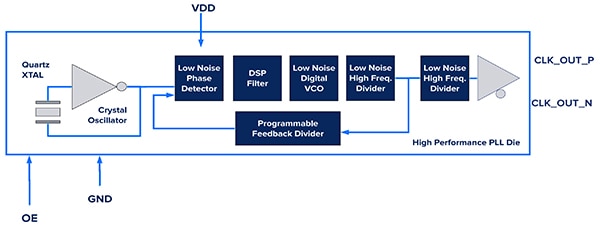

En allmänt använd metod för att generera klockor med låg jitter är att använda en av de många varianterna av PLL-baserade arkitekturer. Enheterna i ClearClock™-familjerna AX5 och AX7 från Abracon finns exempelvis i kapslingar på i 5 x 3,2 mm respektive 5 x 7 mm, och använder en sofistikerad PLL-teknik för överlägset låg jitterprestanda (figur 3).

Figur 3: Klockoscillatorerna AX5 och AX7 från Abracon använder en av de många PLL-baserade konstruktionerna men med subtila förbättringar för att minimera jittret. (Bildkälla: Abracon)

Figur 3: Klockoscillatorerna AX5 och AX7 från Abracon använder en av de många PLL-baserade konstruktionerna men med subtila förbättringar för att minimera jittret. (Bildkälla: Abracon)

Tillsammans med driftfrekvens och oscillatorkonstruktion påverkas jitterprestanda av kvartskristallens fysiska storlek i oscillatorkärnan. När storleken på kristallen minskar blir det allt svårare att tillhandahålla jitterprestanda med överlägsen RMS.

För klockningslösningar i 100 till 200 MHz-bandet, och i mindre format än de PLL-baserade enheterna AX5 och AX7, behövs en ny oscillatorarkitektur. Dessa krav på mindre storlekar är typiskt förknippade med den senaste generationens optiska transceivrar och moduler. Det finns fyra etablerade sätt att konstruera en klockoscillator i intervallet 100 till 200 MHz:

- Använda en kvartsoscillator med ett inverterat mesakvartsämne som resonanselement

- Använda en kvartsoscillator med ett kvartsämne med tredje övertonen som resonanselement

- Använda en oscillatorslinga baserad på ett kvartsämne med tredje överton/fundamentalmod under 50 MHz eller en temperaturkompenserad kristalloscillator på under 50 MHz som är ansluten till en PLL-krets med heltals- eller fraktioneringsläge

- Använda en oscillatorslinga baserad på ett mikroelektromekaniskt system (MEMS) under 50 MHz som är kopplad till en PLL-krets med heltals- eller fraktioneringsläge

Alternativ 1 ger inte den bästa RMS-prestandan för jitter och är inte heller den mest kostnadseffektiva lösningen. Alternativ 3 blir komplicerat och har prestandabrister, medan metoden med MEMS-resonatorer i alternativ 4 inte uppfyller det primära prestandakriteriet på ett jitter med maximal RMS på 200 fs. I alternativ 2 används däremot ett optimalt utformat kvartsämne med tredje övertonen, där hänsyn tas till elektrodernas geometri och optimering av kapningsvinkeln. Denna kombination är optimal när det gäller kostnad, prestanda och storlek.

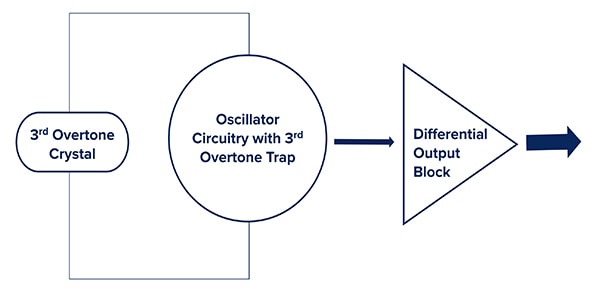

Med hjälp av detta tillvägagångssätt utvecklade Abracon ClearClock-lösningar med en "tredje överton" (figur 4). Enheterna använder en tystare arkitektur för att möjliggöra en prestanda med ett jitter med extremt lågt RMS och och extrem energieffektivitet i miniatyrkapslingar på 2,5 x 2 x 1 mm.

Bild 4: Den "tredje övertonen" i lösningen ClearClock från Abracon använder en tystare arkitektur för att förbättra den övergripande prestandan och energieffektiviteten. (Bildkälla: Abracon)

Bild 4: Den "tredje övertonen" i lösningen ClearClock från Abracon använder en tystare arkitektur för att förbättra den övergripande prestandan och energieffektiviteten. (Bildkälla: Abracon)

I detta system garanterar en noggrann konstruktion av den tredje övertonens kristallyta, tillsammans med korrekt filtrering och "infångning" av den önskade bärsignalen, jitter med enastående RMS-prestanda vid de önskade bärfrekvenserna.

Arkitekturen använder inte en typisk PLL-metod, så det finns ingen uppkonvertering. Det finns därför inget behov av en vanlig fraktionell eller fraktionell eller heltalsmultiplikation för PLL, och den slutliga utgångsfrekvensen har en ett-till-ett korrelation med resonansfrekvensen hos kvartskristallen med den tredje övertonen. Avsaknaden av fraktionell eller heltalsmultiplikation förenklar konstruktionen och möjliggör ett minimalt jitter i minsta möjliga storlek.

Specifikationer och prestanda i verkligheten

Klockoscillatorer består av mer än bara en kristall och dess analoga krets. De inkluderar buffring för att garantera att oscillatorns utgångsbelastning och dess kort- och långsiktiga variationer inte påverkar enhetens prestanda. De har även stöd för olika differentierade digitala logiska utgångsnivåer för kretskompatibilitet. Denna kompatibilitet eliminerar behovet av en extern krets för översättning till logiknivå. En sådan krets skulle öka kostnaden, ta upp mer utrymme och skapa mer jitter.

Eftersom klockoscillatorer används i så många olika tillämpningar med olika matningsspänningar, måste de finnas för en mängd olika matningsspänningar som t.ex. +1,8 V, +2,5 V eller +3,3 V, samt anpassade värden som vanligtvis sträcker sig från 2,25 till 3,63 V. De måste även vara tillgängliga med olika alternativ för utgångar, som t.ex. lågspännings positiv/pseudo emitterkopplad logik(LVPECL) och differentiell signalering med låg spänning (LVDS), samt andra format.

En titt på två familjer av kristallklockoscillatorer, AK2A och AK3A, visar vad som går att åstadkomma genom sofistikerad förståelse och integrering av material, design, arkitektur och test. De två familjerna är snarlika, och de stora skillnaderna består av storlek och maximal frekvens.

Familjen AK2A: Denna familj av kristalloscillatorer finns med nominella frekvenser från 100 till 200 MHz och med matningspänningar på 2,5 V, 3,3 V och 2,25 till 3,63 V med LVPECL, LVDS och HCSL differentialutgångslogik.

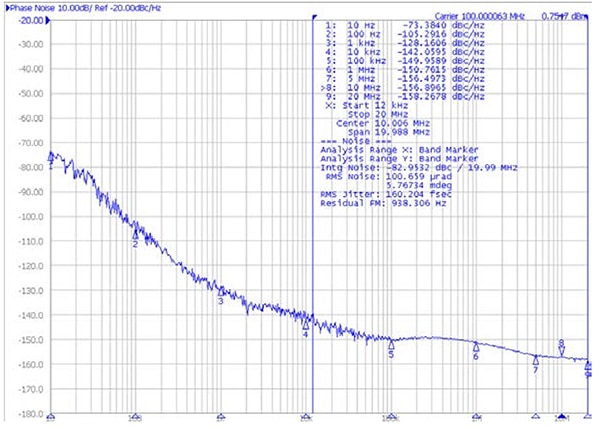

Alla delar i familjen har liknande prestanda, inklusive jitter med lågt RMS. AK2ADDF1-100.000T är exempelvis en enhet för 100 MHz, 3,3 V med LVDS-utgångar och jitter med ett RMS på 160,2 fs (figur 5). Frekvensstabiliteten är utmärkt, bättre än ±15 ppm (delar per miljon) i temperaturområdet, och den levereras i en SMD-kapsling (Surface Mount Device) med sex stift som mäter 2,5 x 2 x 1 mm.

Figur 5: Jittret visar sig vara 160 fs i AK2ADDF1-100.000T, en enhet på 3,3 V, 100 MHz med LVDS-utgångar. (Bildkälla: Abracon)

Figur 5: Jittret visar sig vara 160 fs i AK2ADDF1-100.000T, en enhet på 3,3 V, 100 MHz med LVDS-utgångar. (Bildkälla: Abracon)

Men när klockfrekvenserna ökar måste jittern minska för att prestandan på systemnivå ska bibehållas. För AK2ADDF1-156.2500T, en LVDS-oscillator på 156,25 MHz, sjunker det typiska RMS-värdet för jitter till 83 fs.

Familjen AK3A: Enheterna i familjen AK3A är något större än de i familjen AK2A med ett mått på 3,2 x 2,5 x 1 mm (figur 6). Versioner finns tillgängliga och specificerade för 212,5 MHz, vilket är något högre än gränsen 200 MHz för familjen AK2A.

Figur 6: Kristalloscillatorerna AK3A (höger) är något längre och bredare än serien AK2A (vänster); det finns versioner för frekvenser på upp till 212,5 MHz, jämfört med 200 MHz för AK2A. (Bildkälla: Abracon)

Figur 6: Kristalloscillatorerna AK3A (höger) är något längre och bredare än serien AK2A (vänster); det finns versioner för frekvenser på upp till 212,5 MHz, jämfört med 200 MHz för AK2A. (Bildkälla: Abracon)

De övergripande specifikationerna för denna AK3A-enhet liknar dem för motsvarande komponent i familjen AK2A. Ett exempel är AK3ADDF1-156.2500T3, som är en LVDS-oscillator på 156,25 MHz och ett jitter med ett typiskt RMS på 81 fs, vilket är något bättre än motsvarande medlem i familjen AK2A.

Jittret för båda familjerna varierar beroende på arbetsfrekvens, matningsspänning, kapslingens storlek och val av utgångar.

Ytterligare hänsyn till verkligheten

Det räcker inte med att ha en klockoscillator som fungerar enligt specifikationerna på den dag den lämnar fabriken. Som med alla komponenter, och i synnerhet analoga och passiva komponenter, kan oscillatorerna påverkas över tid på grund av åldrande material och inre påfrestningar.

Denna verklighet är särskilt utmanande för högeffektiva klockoscillatorer, eftersom det inte finns några praktiska eller enkla sätt att korrigera eller kompensera för denna avvikelse genom att lägga till programvara eller smarta kretsar. Det finns dock några sätt att mildra effekterna av avvikelser. Dessa inkluderar långa inbränningsperioder hos slutanvändaren för snabbare åldring av oscillatorn, eller användning av en temperaturstabiliserad oscillator i en ugnsstyrd kapsling. Den första är tidskrävande och en utmaning för leveranskedjan, medan den andra är stor, kostsam och effektkrävande.

Med tanke på att åldrandet är en kritisk parameter har familjen ClearClock från Abracon en strikt, heltäckande frekvensnoggrannhet över hela slutproduktens livslängd på 10 till 20 år. Abracon garanterar att frekvensstabiliteten är bättre än ±50 ppm under denna period. Detta uppnår man genom noggrant urval och tillverkning av kristallen för tredje övertonen och behandling av den för att uppfylla en stabilitet på ±15 från -20 °C till +70 °C och en stabilitet på ±25 ppm från -40 °C till +85 °C.

Som alltid handlar teknik om kompromisser. Serierna AK2A och AK3A från Abracon har förbättrade egenskaper för jitter/störningar jämfört med sina föregångare (generation I av AK2 respektive AX3) genom användning av nästa generations (Gen II) oscillator-ASIC, vilket ger jitteregenskaper med extremt lågt RMS.

Förbättringen uppnås på bekostnad av en något ökad strömförbrukning. Den maximala strömförbrukningen ökar från 50 mA för Gen I till 60 mA för Gen II, även om lågspänningsenheter har ungefär hälften av detta värde. Andra generationens ClearClock-oscillatorer har därför jitter med extremt lågt RMS samtidigt som de har låg strömförbrukning.

Sammanfattning

Oscillatorer för timing är hjärtat i en datalänk eller klockfunktion, och deras noggrannhet, jitter och stabilitet är viktiga parametrar för att uppnå den prestanda som krävs på systemnivå, inklusive högt SNR och låg BER. Högre klockfrekvenser kan uppnås med innovativa materialval och arkitekturer som uppfyller de stränga krav på prestanda som ställs av industrin och dess olika standarder. Serierna AK2A och AK3A från Abracon har jitter under 100 fs i området 100 till 200 MHz i SMD-kapslingar som bara mäter några millimeter på respektive sida.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.