Skapa klockor med lågt jitter och hög frekvens snabbt, med hjälp av en translation loop-modul

Bidraget med av DigiKeys nordamerikanska redaktörer

2021-08-04

Konstruktörer av instrumenterings- och mätsystem behöver störningsfria signaler med lågt jitter för att kunna tillhandahålla det signal-brusförhållande (SNR) eller de felvektorstorlekar (EVM) som krävs för att uppfylla de ständigt ökande kundkraven. Samtidigt, är de pressade att minska kretskortets format, konstruktionskostnad och komplexitet. Det sistnämnda är avgörande för att förkorta utvecklingstiden för att möta de allt snävare tidsramarna för marknadsintroduktion.

Konstruktörer måste, för att hantera de många tillämpningsutmaningarna, omvandla sina lösningar med instrumenterings- och mätningsklockor från specialtillverkade, traditionellt diskreta konstruktioner till mer integrerade lösningar. Ett viktigt steg i detta är att använda en integrerad översättande faslåst loop (PLL). Den gör det möjligt att omvandla frekvensen hos en traditionell VCO-signal (spänningsstyrd oscillator) uppåt, samtidigt som jitter och fasbrus från en fast extern lokal oscillator (LO) i stor utsträckning bibehålls.

Artikeln diskuterar användningen av en translation loop när det gäller att uppnå branschens lägsta integrerade fasbrus. Som exempel presenteras ADF4401A translation loop system i en kapsling (TL SiP) från Analog Devices och visar hur den uppfyller prestandakraven genom en utsignal med integrerad jitterkapacitet för bredbandet på under 10 femtosekunder (fs) rms och förbättrad isolering för att dämpa störande komponenter, samtidigt som den uppfyller konstruktörernas krav på integration, kostnad, komplexitet och tid till marknaden.

Traditionell PLL jämfört med translation loop-funktioner

Det primära syftet med en translation loop är att generera en utsignal som är låst till en inkommande referenssignal med betydligt mindre fasbrus inom bandet jämfört med traditionella PLL:er.

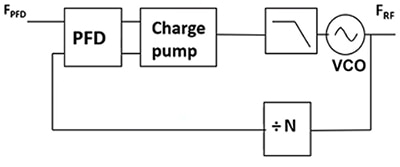

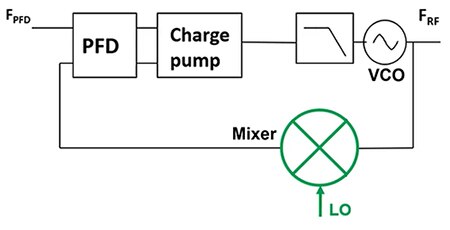

En vanlig PLL består av ett återkopplingssystem som innehåller en fasfrekvensdetektor (PFD), laddningspump, lågpassfilter (LPF), VCO och en frekvensdelare N för återkopplingen (figur 1).

Figur 1: En standard-PLL som låser mot en lägre frekvens (FPFD) och genererar en utgångsfrekvens (FRF). (Bildkälla: Bonnie Baker)

Figur 1: En standard-PLL som låser mot en lägre frekvens (FPFD) och genererar en utgångsfrekvens (FRF). (Bildkälla: Bonnie Baker)

PFD jämför fasen hos ingångens referens och fasen hos den återkopplade signalen och genererar en serie pulser som är proportionella mot fasfelet mellan dem. Laddningspumpen tar emot PFD-pulserna och omvandlar dessa till source- eller sinkpulser för strömmen som i sin tur justerar VCO:n uppåt eller nedåt i frekvens. Lågpassfiltret avlägsnar alla pulsers högfrekvensenergi och omvandlar dem till en spänning som VCO:n kan använda. VCO:ns utsignal matas tillbaka till PFD-blocket genom N-delaren för att slutföra loopen.

Funktionen för frekvensöverföring i figur 1 beräknas med hjälp av ekvation 1:

![]() Ekvation 1

Ekvation 1

Där FRF är utgångens frekvens

N är återkopplingens delningsförhållande (kan vara ett heltal eller en bråkdel)

FPFD är PFD-frekvensen

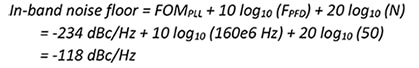

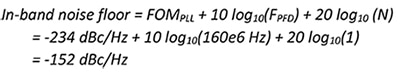

Brusnivån inom bandet i figur 1 beräknas med hjälp av ekvation 2:

![]() Ekvation 2

Ekvation 2

Där FOMPLL är PLL:ens godhetstal (FOM) för fasbrusgolvet inom bandet (FOM)

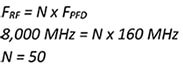

Ta som exempel ett godhetstal för fasbrusgolvet inom bandet på -234 decibel per Hertz (dB/Hz), en PFD-frekvens (FPFD) på 160 MHz och en utgångsfrekvens (FRF) på 8 GHz.

För detta system används ekvation 1 för att beräkna värdet på N:

Ekvation 2 används för att beräkna brusgolvet inom bandet:

I beräkningen ovan bidrar N-delaren starkt till det totala brusgolvet inom bandet, med 20 log10 (50), vilket motsvarar 34 dB. Ett lägre N-värde skulle minska brusgolvet inom bandet, men det skulle även minska utgångens frekvens. Så hur kan vi generera en hög utgångsfrekvens och behålla en lägre loopförstärkning (N)?

Figur 2: För en standard-PLL i detta exempel har bruset från återkopplingsdelaren (20 log10(N)) ett högre brus inom bandet med 34 dB jämfört med den nedre gula bilden där N = 1. (Bildkälla: Bonnie Baker)

Figur 2: För en standard-PLL i detta exempel har bruset från återkopplingsdelaren (20 log10(N)) ett högre brus inom bandet med 34 dB jämfört med den nedre gula bilden där N = 1. (Bildkälla: Bonnie Baker)

Lösningen på detta problem är att ersätta N-delaren med ett mixningssteg som konverterar neråt (figur 3).

Figur 3: En translation loop använder en mixer för att konvertera ner VCO-frekvensen till PFD-frekvensen istället för att använda en traditionell återkopplingsdelare. (Bildkälla: Bonnie Baker)

Figur 3: En translation loop använder en mixer för att konvertera ner VCO-frekvensen till PFD-frekvensen istället för att använda en traditionell återkopplingsdelare. (Bildkälla: Bonnie Baker)

I figur 3 ersätter mixern den återkopplade N-delaren, vilket resulterar i en loopförstärkning som är lika med 1 (N=1). Denna åtgärd kommer att minska återkopplingsloopens bidrag till brusgolvet inom bandet rejält. För beräkning av brus inom bandet är värdet på N nu lika med 1. Med hjälp av ekvation 2 är brusgolvet inom bandet för det modifierade systemet följande:

Det nya bruset inom bandet visar en förbättring på 34 dBc/Hz.

I figur 3 är mixern beroende av en LO med extremt lågt brus, även kallad Offset LO. FLO ±FRF måste vara lika med FPFD för att uppnå låsning.

Med translation loop-arkitekturen är fasbruset hos Offset LO mycket viktigt för att uppnå bästa prestanda vid RF-utgången. Därför konstrueras vanligtvis en offset-LO baserat på spänningsstyrda akustiska ytvågor (SAW), oscillatorer (VCSO:er), kamgeneratorer eller dielektriska resonatoroscillatorer (DROs). OBS! Kontakta Analog Devices om du vill ha hjälp med att konstruera en Offset LO.

Utmaningar i samband med användning av en translation loop

Traditionellt sett innebär konstruktionen av en translation loop med lågt brus, implementering av många kretsblock, vilket medför en komplicerad konstruktion, som vanligtvis är stor och med begränsad flexibilitet. Dessutom måste hela kretsen valideras och karakteriseras för den avsedda driften. Ett stort problem vid konstruktionen är till exempel LO-läckage (LO till RF-isolering) till RF-utsignalen. Detta är en stor utmaning för konstruktörer att hantera. Med traditionella konstruktioner brukar konstruktörerna fortsätta med flera konstruktionsiterationer för att uppnå en optimerad prestanda och lämplig isolering.

Figur 3 visar hur ADF4401A integrerar viktiga kretsblock för att ge en fullt karakteriserad lösning och eliminera de traditionellt svåra områdena med avseende på prestanda och isolering i konstruktioner av en translation loop. Denna programmerbara lösning gör det möjligt för konstruktörer att uppnå optimerad prestanda redan vid det första försöket och minska tiden till marknaden.

Utvärdering av ADF4401A

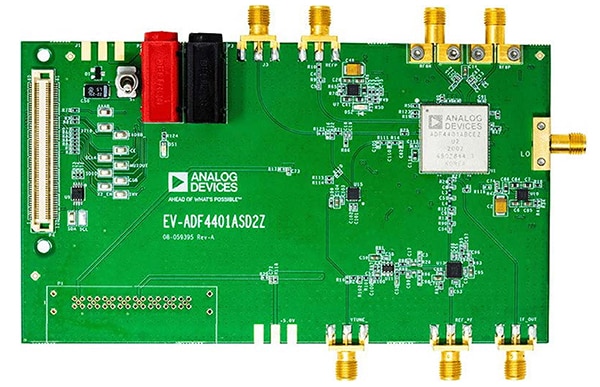

ADF4401A är utformad för att hjälpa konstruktörer att förkorta tiden till marknaden för högeffektiv instrumentering, med hjälp av en lösning för generering av frekvenser som har en RF-bandbredd på 62,5 MHz till 8 GHz. Genom att använda en mixer som konverterar nedåt, har ADF4401A ett mycket lågt brus inom bandet och ett bredbandigt jitter på ~9 femtosekunder (fs) integrerat från 100 Hz till 100 MHz. Konstruktions- och layoutteknikerna inuti ADF4401A möjliggör ett typiskt störningsfritt dynamiskt område på 90 dBc. En kapslingsstorlek på 18 x 18 x 2,018 millimeter (mm) minskar kretskortsutrymmet betydligt jämfört med en traditionell diskret konstruktion.

För att utvärdera enhetens prestanda kan konstruktörer använda utvärderingskortet EV-ADF4401ASD2Z (figur 4). Kortet innehåller en komplett translation loop, inklusive en extern PFD (HMC3716), ett aktivt filter (LT6200) och en multiplexer (ADG1609).

Figur 4: Utvärderingskortet EV-ADF4401ASD2Z för translation loop-modulen ADF4401A innehåller en extern PFD, ett USB-gränssnitt och spänningsregulatorer. (Bildkälla: Analog Devices)

Figur 4: Utvärderingskortet EV-ADF4401ASD2Z för translation loop-modulen ADF4401A innehåller en extern PFD, ett USB-gränssnitt och spänningsregulatorer. (Bildkälla: Analog Devices)

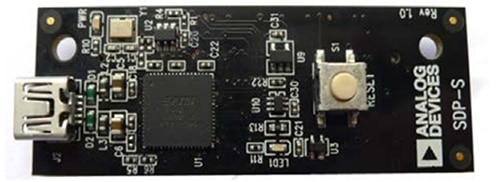

EV-ADF4401ASD2Z innehåller ADF4401A TL SiP med integrerad VCO, ett loopfilter (5 MHz), en PFD, ett USB-gränssnitt och spänningsregulatorer. Därutöver kräver EV-ADF4401ASD2Z styrkortet EVAL-SDP-CS1Z (SDP-S) för systemdemonstrationsplattformen (SDP) (seriell) (figur 5). Kortet tillhandahåller en USB-anslutning från en PC till EV-ADF4401ASD2Z så att den kan programmeras. Styrkortet ingår inte i satsen EV-ADF4401ASD2Z.

Figur 5: Styrkortet EVAL-SDP-CS1Z (eller SDP-S) krävs för att tillhandahålla en USB-anslutning från EV-ADF4401ASD2Z till en PC för programmering. (Bildkälla: Analog Devices)

Figur 5: Styrkortet EVAL-SDP-CS1Z (eller SDP-S) krävs för att tillhandahålla en USB-anslutning från EV-ADF4401ASD2Z till en PC för programmering. (Bildkälla: Analog Devices)

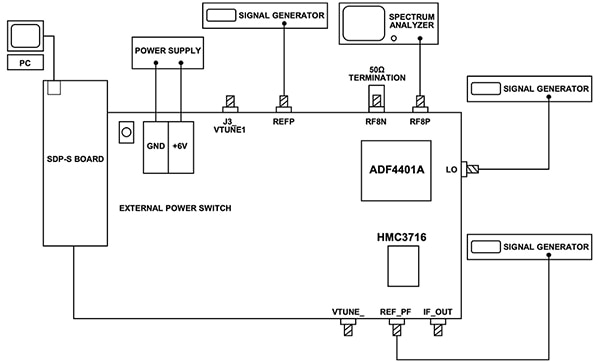

Figur 6 visar de fysiska anslutningarna för systemet EV-ADF4401ASD2Z. Den tillhörande programvaran Analysis | Control | Evaluation (ACE för analys, styrning och utvärdering) kontrollerar TL SiP-funktionerna. Ström kommer från en extern strömförsörjning på 6 V.

Figur 6: Ett konfigurationsdiagram för EV-ADF4401ASD2Z som visar den utrustning och de anslutningar som krävs för att utvärdera ADF4401A, inklusive styrkortet SDP-S, en PC, strömförsörjning, signalgeneratorer och en spektrumanalysator. (Bildkälla: Analog Devices)

Figur 6: Ett konfigurationsdiagram för EV-ADF4401ASD2Z som visar den utrustning och de anslutningar som krävs för att utvärdera ADF4401A, inklusive styrkortet SDP-S, en PC, strömförsörjning, signalgeneratorer och en spektrumanalysator. (Bildkälla: Analog Devices)

Den föreslagna utrustningen för utvärderingskortet inkluderar en PC med Windows, en spektrumanalysator eller en analysator för signalkällan och tre signalgeneratorer.

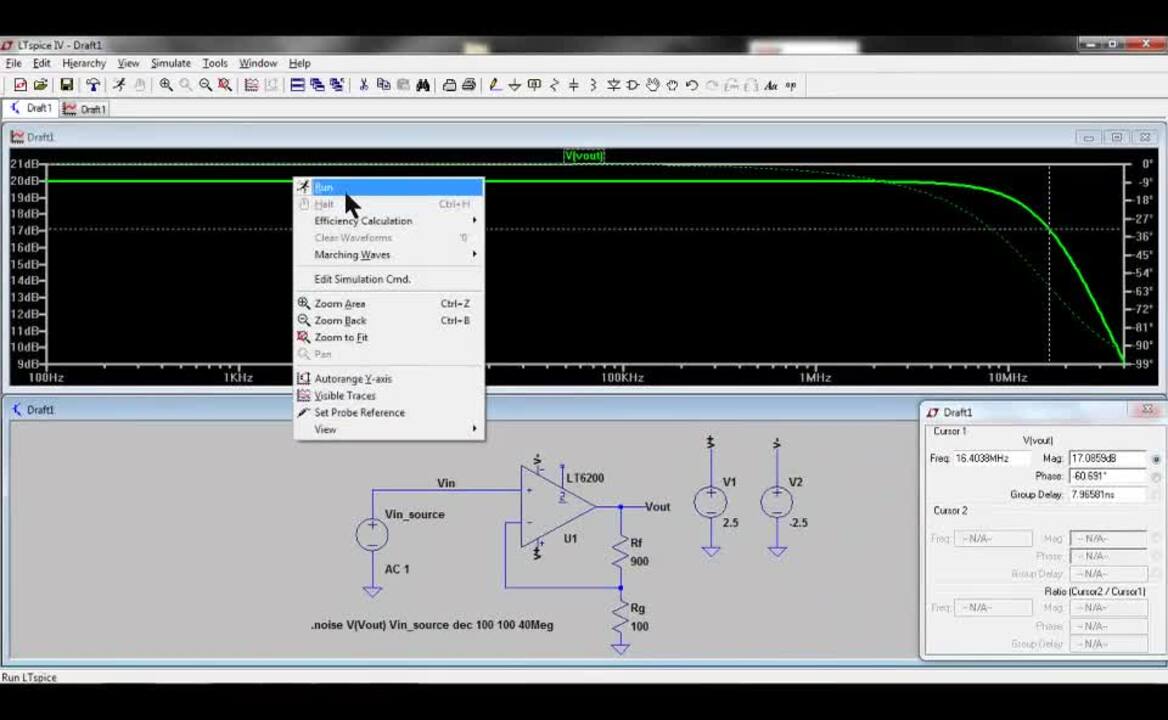

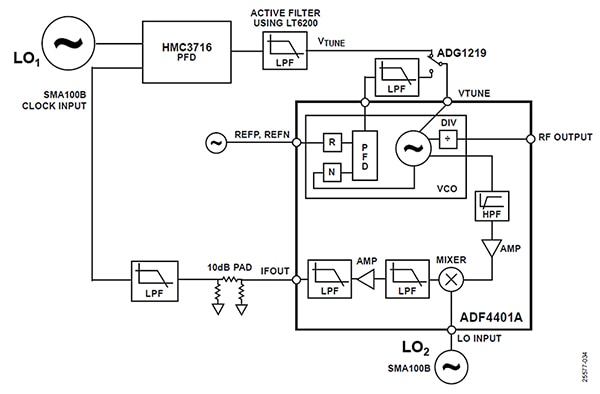

Blockdiagrammet för EV-ADF4401ASD2Z visar modulen ADF4401A tillsammans med Analog Devices PFD HMC3716, operationsförstärkare LT6200 och SPDT-omkopplare ADG1219 (figur 7).

Figur 7: Blockdiagrammet för utvärderingskortet EV-ADF4401ASD2Z visar de viktigaste komponenterna som stöder AD4401A translation loop. (Bildkälla: Analog Devices)

Figur 7: Blockdiagrammet för utvärderingskortet EV-ADF4401ASD2Z visar de viktigaste komponenterna som stöder AD4401A translation loop. (Bildkälla: Analog Devices)

Det är viktigt att använda en PFD som kan arbeta med höga frekvenser eftersom detta minimerar behovet av delare, som kan försämra brusresponsen inom bandet. Frekvenskapaciteten för fasjämförelse på 1,3 GHz hos HMC3716 från Analog Devices, gör den perfekt för användning i IF-området för ADF4401A. En sådan krets som kan jämföra både frekvens och fas eliminerar behovet av ytterligare kretsar för att styra frekvensen till den avsedda utgångsfrekvensen. HMC3716 blir den externa PFD:n som slutför offsetloopen. Det högfrekventa driftområdet och det extremt låga fasbruset i HMC3716 gör det möjligt att konstruera loopfilter med stor bandbredd.

I figur 7 dämpar operationsförstärkaren LT6200 högfrekventa trunkeringsstörningar, med en LPF-konfiguration, medan omkopplaren ADG1219 avslutar systemets translation loop.

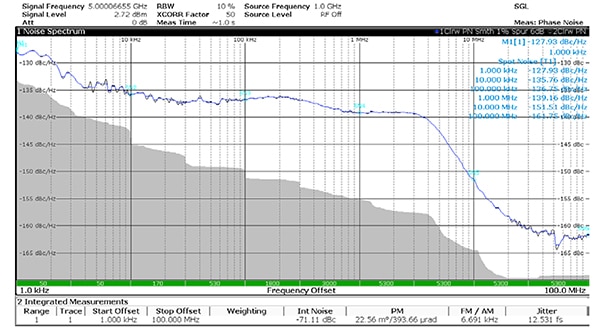

Utvärderingsfixturen EV-ADF4401ASD2Z skapar brusdiagram och jittermätningar inom bandet enligt vad som visas i figur 8.

Figur 8: Fasbrus i ett enstaka sidoband på 5 GHz utgången, med en extern HMC3716-referens på 500 MHz och extern LO på 4,5 GHz. (Bildkälla: Analog Devices)

Figur 8: Fasbrus i ett enstaka sidoband på 5 GHz utgången, med en extern HMC3716-referens på 500 MHz och extern LO på 4,5 GHz. (Bildkälla: Analog Devices)

I figur 8 består ingången för LO2 och HMC3716, av en SMA100B signalgenerator för RF- och mikrovågor. Utvärderingskortets LO2-brus inom bandet är ungefär -135 dBc/Hz, vilket är tydligt vid låga offsets upp till 300 kHz. LO2, modulen ADF4401A, PFD:n HMC3716 och loopfiltret bidrar till ett brus inom bandet på cirka -140 dBc/Hz. Det interna fasbruset uppträder mellan 5 och 50 MHz, och faskanalen har ett fasbrusgolv på cirka -160 dBc/Hz. Tillsammans ger detta ett rms-jitter på totalt 12,53 fs.

Sammanfattning

Instrumenteringssystem för höga hastigheter kräver klockor med extremt lågt jitter för att garantera att utdata inte äventyras. Utmaningen för konstruktörer är att hitta lämpliga enheter att bygga den snabba gigahertz-klockan med. En ADF4401A-translation loop förenklar valet av enhet för att bygga klocksystemet med avsevärt, och tillhandahåller en kompakt modul som garanterar lågt jitter vid högre frekvenser, samtidigt som utrymmesbehovet på kretskortet, kostnaden och tiden för marknadsintroduktion minskar.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.