Maximera effekttätheten och prestandan med dubbla MOSFET:ar i tillämpningar med switchande omvandlare

2024-02-27

Switchande omvandlare och motordrivenheter för industri- och fordonstillämpningar kräver MOSFET:ar (fälteffekttransistorer av kiselmetalloxid) som är små, effektiva och genererar minimalt med elektriska störningar. En dubbel MOSFET bidrar till att uppfylla dessa krav.

Genom att placera två MOSFET:ar i en och samma kapsling upptar välkonstruerade dubbla MOSFET:ar mindre plats på kretskortet, minskar den parasitiska induktansen och eliminerar behovet av skrymmande och kostsamma kylflänsar för att förbättra den termiska prestandan. Enheterna kan switcha vid flera hundra kilohertz utan störningar, arbeta stabilt i ett stort temperaturområde och uppvisa låga läckströmmar. Konstruktörer måste dock förstå deras driftsegenskaper för att kunna utnyttja fördelarna fullt ut.

Artikeln ger exempel på dubbla MOSFET:ar från Nexperia och visar hur konstruktörer kan använda dem för att klara utmaningarna med robusta, högeffektiva konstruktioner i begränsade utrymmen. Artikeln diskuterar olika tillvägagångssätt för att optimera kretsarnas och kretskortens konstruktion och tipsar om elektrotermisk simulering och förlustanalys.

Högre verkningsgrad vid hög switchningshastighet

Dubbla MOSFET:ar passar för många fordons- (AEC-Q101) och industritillämpningar, inklusive DC/DC-omvandlare, växelriktare för motorer och styrenheter för magnetventiler. I tillämpningar kan dubbla MOSFET:ar bland annat användas i topologikonfigurationer med switchande par och halvbryggor.

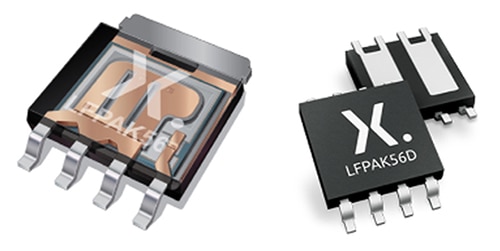

Serien LFPAK56D från Nexperia är ett intressant exempel på dubbla MOSFET:ar. Den använder en teknologi med kopparöverföringar från Nexperia som har enastående strömkapacitet, en kapsling med låg impedans och hög tillförlitlighet (figur 1, höger). De solida kopparöverföringarna förbättrar värmeavledningen från halvledarsubstratet via lödfogarna till kretskortet så att ca 30 % av den totala värmeavledningen kan ske genom anslutningsstiften. De stora tvärsnitten av koppar minskar även den resistiva effektavledningen och dämpar ringningar genom att minska den parasitiska ledningsinduktansen.

Figur 1: LFPAK56D-kapslingarna (höger) integrerar två oberoende MOSFET:ar och använder kopparöverföringar som liknar LFPAK56-kapslingen med en MOSFET (vänster). (Bildkälla: Nexperia)

Figur 1: LFPAK56D-kapslingarna (höger) integrerar två oberoende MOSFET:ar och använder kopparöverföringar som liknar LFPAK56-kapslingen med en MOSFET (vänster). (Bildkälla: Nexperia)

Liksom de flesta komponenter avsedda för switchande omvandlare med hög spänning använder LFPAK56D superjunction-teknologi. Konstruktionen minskar drain-source-resistansen i påslaget tillstånd (RDS(on)) och gate-drain-laddningen (QGD), vilket minimerar effektförlusterna. Användning av två MOSFET:ar på samma substrat minskar drain-source-resistansen ytterligare.

Som MOSFET:ar med superjunction-teknologi är serien LFPAK56D motståndskraftig mot lavinhändelser och har ett brett område för säker drift (SOA). Till exempel har respektive MOSFET på 100 V i TrenchMOS:en PSMN029-100HLX en RDS(on) på 29 mΩ, klarar 68 W och kan släppa igenom upp till 30 A.

Serien LFPAK56D använder även teknologin SchottkyPlus från NXP för att minska beteendet vid transienter och läckströmmen. Till exempel är den typiska RDS(on) för PSMN014-40HLDX normalt 11,4 mΩ, och läckströmmen för drain-source är på extremt låga 10 nA.

För att kunna utnyttja de höga strömstyrkorna i MOSFET:arna fullt ut, måste kretskortet vara konstruerat för att avleda hög värme och säkerställa stabila elektriska anslutningar. Kretskort med flera lager och tillräckligt många vior samt stora, breda kopparledningsbanor garanterar hög termisk prestanda.

Undvik termisk instabilitet

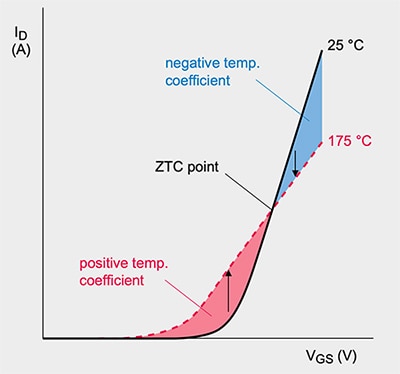

Även om helt tillslagna effekt-MOSFET:ar är termiskt stabila, finns det en risk för termisk instabilitet när dräneringsströmmen (ID) är låg.I detta driftläge tenderar lokal uppvärmning att sänka gränsvärdet för gate-source-spänningen (VGS(th)), vilket innebär att enheten aktiveras snabbare. Detta skapar en positiv återkopplingssituation där den extra strömmen orsakar mer uppvärmning och en ännu lägre VGS(th).

Figur 2 påvisar effekten för en konstant drain-source-spänning (VDS). När VGS ökar finns det en kritisk ID som kallas för nolltemperaturkoefficient (ZTC). Över denna ström finns det en negativ återkoppling och termisk stabilitet (blå zon); under den dominerar spänningsfallsgränsen, vilket medför termiskt instabila driftstillfällen som kan leda till termisk rusning (röd zon).

Figur 2: Under nolltemperaturkoefficienten kan MOSFET:ar hamna i termisk instabilitet på grund av en termiskt inducerad sänkning av VGS (rött område). (Bildkälla: Nexperia)

Figur 2: Under nolltemperaturkoefficienten kan MOSFET:ar hamna i termisk instabilitet på grund av en termiskt inducerad sänkning av VGS (rött område). (Bildkälla: Nexperia)

Effekten minskar det säkra driftområdet vid låga strömmar och höga drain-source-spänningar. Detta är inte ett stort problem vid snabba switchningar med en brant dV/dt-flank. Men när omkopplingstiden ökar, t.ex. för att minska elektromagnetiska störningar, blir den termiska instabiliteten mer sannolik och potentiellt farlig.

Lägre switchningsförluster vid höga frekvenser

När man väljer en MOSFET med superjunction-teknologi för tillämpningar med snabba switchningar är det viktigt med en låg QGD, eftersom det minskar switchningsförlusterna avsevärt.

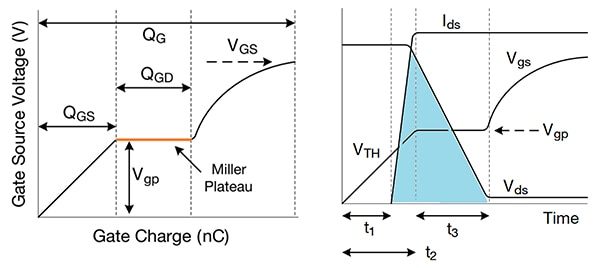

Höga effektförluster uppstår vid switchning när betydande spännings- och strömförändringar inträffar samtidigt mellan drain, gate och source. Låg QGD resulterar i en kort Miller-platå (figur 3, vänster), vilket leder till en brant switchningsflank (dVds/dt) och i slutänden en lägre dynamisk energiförlust vid inkoppling (figur 3, blått område till höger).

Figur 3: En kort Miller-platå (vänster) innebär en brant switchningsflank, vilket resulterar i låga dynamiska förluster (blått område till höger). Vgp är gate-source-spänningen för Miller-platån, VTH är gränsspänningen för gate och IDS är drain-source-strömmen. (Bildkälla: Vishay)

Figur 3: En kort Miller-platå (vänster) innebär en brant switchningsflank, vilket resulterar i låga dynamiska förluster (blått område till höger). Vgp är gate-source-spänningen för Miller-platån, VTH är gränsspänningen för gate och IDS är drain-source-strömmen. (Bildkälla: Vishay)

Begränsning av lavinenergi och skydd för MOSFET:en

När en statorspole i en tillämpning med motordrivenheter stängs av upprätthåller det kollapsande magnetfältet strömflödet och genererar en hög induktionsspänning över MOSFET:en som överlagras på matningsspänningen (VDD). Den omvända nedbrytningsspänningen (VBR) hos MOSFET:ens backdiod begränsar dock denna höga spänning. I den så kallade lavineffekten omvandlar MOSFET:en den utströmmande magnetiska energin till lavinenergi (EDS) tills strömmen för spolen sjunker till noll. Detta kan snabbt leda till överhettning av halvledarens kristall.

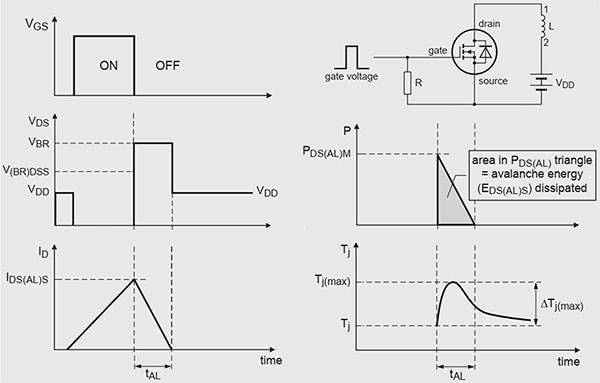

Figur 4 visar en enkel styrning av en spole med en MOSFET-switch och tidssignalerna före, under (tidsfönster tAL) och efter en enda lavinhändelse. Om den avledda lavinenergin (EDS(AL)S) är för hög kommer den värme som bildas att skada halvledarens struktur.

Figur 4: Tidssignaler för en MOSFET före, under (tAL) och efter en enda lavinhändelse. (Bildkälla: Nexperia)

Figur 4: Tidssignaler för en MOSFET före, under (tAL) och efter en enda lavinhändelse. (Bildkälla: Nexperia)

MOSFET:en LFPAK56D är konstruerad för att vara mycket robust och klarar flera miljarder lavinhändelser utan skador enligt laboratorietester utförda av Nexperia. Med tanke på den maximala lavinenergin kan spolens drivkretssteg avleda med ytterligare back- eller låsningsdioder och endast använda lavinfunktionen hos MOSFET:arna.

Elektrotermisk simulering online

För att förbättra systemets effektivitet räcker det inte med att förlita sig på ett enkelt godhetstal (FOM), som t.ex. produkten av RDS x QGD. Istället måste konstruktörer genomföra en mer exakt förlustanalys som tar hänsyn till MOSFET-förluster till följd av:

- Konduktivitet vid tillkoppling

- Till- och frånkopplingsförluster

- Laddning och urladdning av utgångskapacitansen

- Kontinuitets- och kopplingsförluster för backdioden

- Laddning och urladdning av gate-kapacitansen

För att minimera de totala förlusterna måste konstruktörer förstå sambandet mellan MOSFET-parametrarna och driftmiljön. Nexperia har för detta ändamål elektrotermiska precisionsmodeller för MOSFET:ar som kombinerar elektrisk och termisk prestanda och representerar alla viktiga beteenden för MOSFET:arna. Utvecklare kan använda simuleringsverktyget PartQuest Explore online eller importera modellerna i formaten SPICE och VHDL-AMS till valfri simuleringsplattform.

I skrivande stund är de elektriska modellerna endast tillgängliga för MOSFET:arna LFPAK56D. Därför används en annan MOSFET-modell för följande exempel av termisk simulering, nämligen BUK7S1R0-40H.

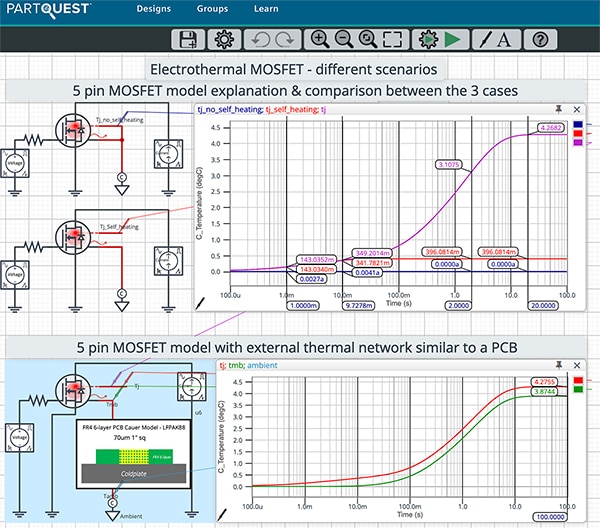

Det interaktiva experimentet IAN50012 elektrotermiska modeller för effekt-MOSFET:ar simulerar tre uppvärmningsscenarier för MOSFET:en BUK7S1R0-40H efter att en strömlast på 36,25 A har kopplats in. Figur 5 visar de tre simuleringsuppsättningarna till vänster.

Figur 5: Här visas en elektrotermisk simulering av en MOSFET med hjälp av simuleringsverktyget PartQuest Explore online. (Bildkälla: Nexperia)

Figur 5: Här visas en elektrotermisk simulering av en MOSFET med hjälp av simuleringsverktyget PartQuest Explore online. (Bildkälla: Nexperia)

I det övre exemplet "tj_no_self_heating" är anslutningen och monteringssockeln direkt kopplade till omgivningstemperaturen (Tamb) på 0 °C utan värmeresistans (Rth). I exemplet i mitten, "tj_self_heating", är kretsen kopplad via Rth-j och Tj stiger med cirka 0,4 °C. Det nedre exemplet visar en monteringssockel (mb) som är kopplad till omgivningstemperaturen via Rth_mb på ett FR4-kort med sex lager och en kylfläns. Tmb (grön) stiger till 3,9 °C och Tj (röd) stiger till 4,3 °C.

Sammanfattning

MOSFET:en LFPAK56D med extremt låga förluster har en mycket bra verkningsgrad och effekttäthet i snabbt switchande omvandlare eller motordrivenheter. Överväganden för kretsarnas och kretskortens termiska utformning och den elektrotermiska simulering som diskuteras här illustrerar hur konstruktörer kan hantera utmaningarna med robusta, högeffektiva konstruktioner för begränsade utrymmen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.