Varför det är så enkelt att ansluta integrerade kretsar med Inter-Integrated Circuit-bussen (I2C) – och hur den ska användas

Bidraget med av DigiKeys nordamerikanska redaktörer

2020-04-07

Kommunikation och styrning mellan integrerade kretsar med en parallell buss på ett kretskort är inte praktiskt. Även en 8-bitarsprocessor skulle kräva 16 ledningar bara för data och många fler för en adressbuss. Det är ännu mer problematiskt om flera integrerade kretsar måste finnas på en delad kommunikationsbuss. Det finns inte tillräckligt med utrymme för alla dessa ledningsbanor på kretskortet. Lösningen är att länka integrerade kretsar med en seriell kommunikationsbuss som Inter-Integrated Circuit-bussen (I2C), en seriell buss med två ledningar som löser problemet.

I den här artikeln beskrivs ursprunget för I2C-bussen och hur den fungerar för att ge en effektiv seriell länk mellan integrerade kretsar. Därefter går vi igenom hur I2C-bussen implementeras fysiskt, protokollstrukturen och vanliga tillämpningar för denna vanligt föerkommande kommunikationsbuss. Exempel på I2C-gränssnitt och lösningar från Microchip Technology används i demonstrationssyfte. I artikeln tar vi även upp likheter och skillnader för I2C med System Management Bus (SMBus).

Vad är I2C-bussen?

I2C-bussen utvecklades av Phillips Semiconductors, nu NXP Semiconductors, i början av 1980-talet som en enkel dubbelriktad tvåledningsbuss för effektiv kommunikation och styrning av integrerade kretsar på ett vanligt kretskort. Den första specifikationen slutfördes 1992 och bussen har sedan dess blivit faktisk standard i komponenter från drygt 50 tillverkare av integrerade kretsar. Den stora spridningen möjliggör konstruktion med ett systemsynsätt, där integrerade kretsar snabbt kan inkluderas i I2C-busstrukturen utan att det kräver specialkonstruktioner. Flera andra specialiserade bussar, som SMBus och Power Management Bus (PMBus) med flera, delar grundarkitekturen.

I2C-bussen kan länka flera integrerade kretsar och sensorer eftersom det är en adresserbar buss, där ett sju- eller tiobitars adressfält gör så att meddelanden kan skickas till en vald enhet via masterenheten. Den ursprungliga I2C-bussen hade en maximal klockfrekvens på 100 kHz men under åren har driftlägen med högre hastighet höjt den gränsen till 3,4 MHz.

I2C-bussen använder en seriell dataledning med två ledare, eller SDA, och en seriell klockledare, eller SCL, med två ledare. SDA och SCL är dubbelriktade ledningar med öppen drain/kollektor och är anslutna till den positiva strömbussen via en strömkälla eller ett pullup-motstånd. Flera enheter kan anslutas till bussen, där det högsta antalet begränsas av bussens kapacitans. En masterenhet styr bussen och varje enhet på bussen har en unik adress. Masterenheten kan både sända och ta emot data via bussen (figur 1). I2C stöder drift med flera masterenheter som har kollisionsdetektering och medling för att förhindra att två eller flera masterenheter initierar dataöverföringar samtidigt. Men den här artikeln fokuserar på konfigurationer med en masterenhet.

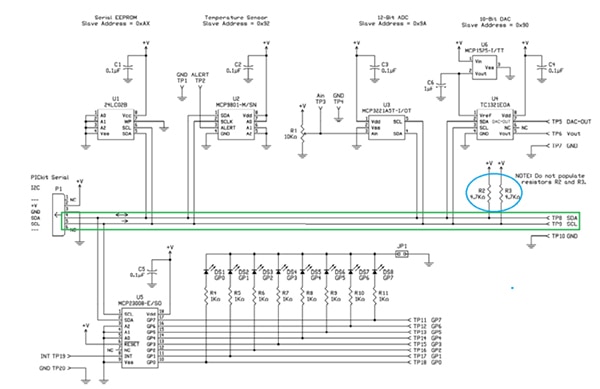

Figur 1: Schema över ett demokretskort från Microchip Technology som implementerar I2C-bussen och ansluter den till fem olika enheter. Masterenheten ligger utanför kortet genom kontaktdon 1. SCL- och SDA-ledningarna har grön kontur och de två pullup-motstånden är inringade i blått. (Bildkälla: Microchip Technology)

Figur 1: Schema över ett demokretskort från Microchip Technology som implementerar I2C-bussen och ansluter den till fem olika enheter. Masterenheten ligger utanför kortet genom kontaktdon 1. SCL- och SDA-ledningarna har grön kontur och de två pullup-motstånden är inringade i blått. (Bildkälla: Microchip Technology)

Figur 1 visar schemat för ett PKSERIAL-I2C1 I2C-demokort från Microchip Technology. Kortet implementerar I2C-bussen med fem olika enheter, så som en EEPROM, en temperatursensor, en 12-bitars analog-till-digital-omvandlare (A/D-omvandlare), en 10-bitars digital-till-analog-omvandlare (D/A-omvandlare) och en 8-bitars seriell-till-parallell-omvandlare. Masterenheten finns inte på kortet och ansluts via kontaktdon P1. SCL- och SDA-busslinjerna har grön kontur och pullup-motstånden är inringade i blått.

SDA- och SCL-nivåerna är, generellt, en fast andel av den positiva matningsspänningen, normalt betecknad VDD. Referensnivåerna är inställda på 70 % och 30 % av VDD för logik ”1” (hög) respektive logik ”0” (låg).

Klocksignaler sker i pulser med en klockning för varje överförd databit. Data på SDA-ledningen måste vara giltig medan klockan är hög. Data kan bara ändras när klockan är låg.

Ur en konstruktörs synvinkel förenklas nya projekt eftersom I2C-gränssnitten är integrerade i de integrerade kretsarna och det finns inget behov av att konstruera ett gränssnitt. Varje enhet ansluts helt enkelt direkt till bussen. Integrerade kretsar kan läggas till och tas bort från bussen utan att det påverkar de andra kretsarna (förutsatt att det totala antalet integrerade kretsar inte överskrider kapacitansgränsen). Den enkla tvåledningsbussen minimerar antalet stift på varje integrerad krets och antalet körningar på kretskortet.

I2C-protokollet

Bussen är 8-bitarsorienterad, med kommunikation i bytes. Som nämnts, var den ursprungliga klockfrekvensen 100 kHz i vad som nu refereras till som Standard Mode (standardläge). Bussen stöder nu 400 kbit/s i Fast Mode (snabbt läge), upp till 1 Mbit/s i Fast Mode Plus (snabbt läge plus) och upp till 3,4 Mbit/s i High Speed Mode (Hs-Mode, höghastighetsläge).

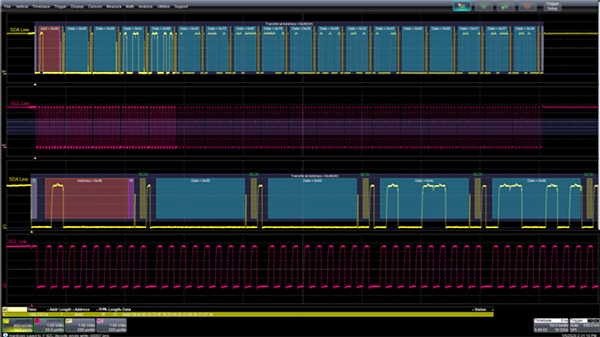

I2C-protokollet illustreras bäst genom att titta på en typisk överföring på bussen (figur 2). Källan till skärmbilden är ett Teledyne LeCroy-oscilloskop med seriell datatrigger med låg hastighet och avkodningsalternativet WS4KHD-EMB TD. Det här oscilloskopsalternativet kan trigga och avkoda upp till 19 seriella datagränssnitt med låg hastighet, inklusive I2C.

Figur 2: Ett typiskt I2C-datapaket bestående av startbit, adressfält, bekräftelsebit (ACK), 17 databyte var och en med en egen ACK-bit och slutligen en stoppbit. Varje fält identifieras av ett färgkodat överlägg. Den övre (gula) grafen är hela SDA-paketet, under den är SCL-klockan (röd). Den tredje och fjärde grafen är vågrätt expanderade vyer av båda signalerna. (Bildkälla: DigiKey)

Figur 2: Ett typiskt I2C-datapaket bestående av startbit, adressfält, bekräftelsebit (ACK), 17 databyte var och en med en egen ACK-bit och slutligen en stoppbit. Varje fält identifieras av ett färgkodat överlägg. Den övre (gula) grafen är hela SDA-paketet, under den är SCL-klockan (röd). Den tredje och fjärde grafen är vågrätt expanderade vyer av båda signalerna. (Bildkälla: DigiKey)

Oscilloskopet kan utlösas vid specifika seriella händelser som start, stopp, saknad bekräftelse (ACK), adress, adress plus data, ramlängd och EEPROM-dataöverföring. Protokollelementen för den seriella datastandarden identifieras av ett färgkodat överlägg. Varje protokollfält avkodas i binär, hex eller ASCII med den valda koden visad i överlägget.

SDA-signalen visas som en gul graf och SCL-signalen visas som en röd graf. Den grå överläggsrutan anger start- och stoppfunktionen. Det tegelröda överlägget markerar adressdata, det blå fältet är paketdata och de olivgröna överläggsrutorna markerar ACK-funktionerna.

Den översta grafen visar hela I2C SDA-paketet från start till stopp. Direkt under den är den motsvarande SCL-signalen. Den tredje grafen uppifrån är en tidsexpanderad zoomgraf för SDA-signalen och under det finns den synkrona SCL-signalen.

Både SDA- och SCL-ledningen vilar i högt tillstånd mellan överföringar när bussen är ledig. SCL-signalen består av omgångar med nio pulser i klockfrekvensen, en för varje bit som överförs och en ytterligare för ACK-biten.

Alla busstransaktioner börjar med en mastergenererad startbit som i den zoomade SDA-grafen visas som en gråfärgad överläggsruta. Start anges av att mastern drar SDA-linjen lågt medan SCL-linjen är i ett högt tillstånd. När mastern utfärdar startbiten anses bussen vara upptagen. Mastern kan utfärda flera starter, en situation där de efterföljande starterna ofta kallas omstarter.

Alla dataöverföringar är 8 bitar (en byte) i längd, var och en följd av en ACK-bit. Bitar sänds med den mest betydelsefulla biten (MSB) först. Varje byteöverföring måste bekräftas. Om slavenheten är upptagen och inte kan ta emot eller sända data kan den dra SCL-linjen lågt. Det tvingar in masterenheten i ett väntetillstånd tills slavenheten frisläpper SCL-linjen.

ACK-biten bildas när den sändande enheten frisläpper SDA-linjen innan den nionde bekräftelseklockpulsen. Om den mottagande enheten har tagit emot databyten, drar den ned SDA-ledningen. I zoomvyn för SDA:n i figur 2 finns det en smal topp precis innan den nionde klockpulsen, vilket är SDA-ledningen som frisläpps för att återgå till högt tillstånd. Mottagaren drar ned SDA-ledningen och genererar ACK-signalen, som markeras symboliskt av den olivgröna överläggsrutan. Om mottagaren inte drar ned SDA-ledningen innan den nionde klockpulsen, är det ett negativ bekräftelse-svar (NACK). Om NACK inträffar kan mastern generera en stoppsignal och avbryta överföringen eller utfärda en upprepad start för att försöka igen.

Direkt efter starttillståndet utfärdas en slavadress. Det anges med en tegelröd överläggsruta. Det finns två möjliga adressformat, 7 eller 10 bitar, där 7-bitarsadressen är den vanligaste. De första 7 bitarna efter starten representerar adressdata. Den 8:e biten anger datariktningen – läsning eller skrivning. En skrivning anges av att SDA-ledningen är i lågt tillstånd och om SDA-ledningen är i högt tillstånd då anger det en läsåtgärd. 10-bitarsadressering använder de första två bytesen efter starttillståndet. I2C reserverar flera adresser för interna funktioner. Avkodningsadressen visas i adressöverläggsrutan i binärt format, hex- eller ASCII-format.

De blå överläggsfälten markerar dataöverföringarna. Vart och ett är åtta bitar långt och följs av ett ACK-/NACK-svar. Antalet databyte i ett I2C-paket är obegränsat, men figur 2 innehåller 17. Avkodad data, som adressavkodningen, visas i dataöverläggsrutan. Dataströmmen följs av en mastergenererad stoppbit i slutet av dataöverföringen, angiven med en grå överläggsruta i det översta dataspåret. Stoppbiten är en låg-till-hög-övergång på SDA-linjen medan SCL-linjen är i högt tillstånd. Efter stoppsignalen är bussen ledig igen.

Tabellen längst ned sammanfattar all information om det relaterade datapaketet, som tid efter trigger, adresslängd, adress, läs- eller skrivåtgärd, paketlängd och en sammanfattning av datainnehållet. Antalet poster i tabellen matchar antalet I2C-paket som registrerats av oscilloskopet, vilket i det här fallet bara är en enda ledning.

Om det inträffar ett protokollfel anges det med en klarröd ruta bakom de andra protokollöverläggsrutorna.

I2C-enheter

En av de största fördelarna med I2C-bussen är det extremt stora antalet enheter som har den inbyggd i konstruktionen. Microchip Technologies-demokortet har några exempel på de olika typer av integrerade kretsar som innehåller I2C-bussen eller någon buss som bygger på dess teknik, som SMBus.

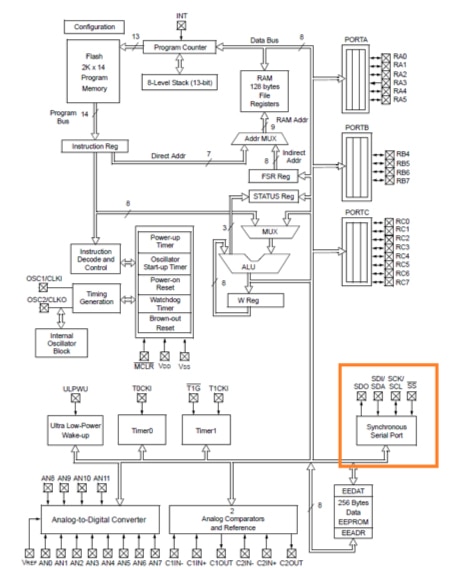

Microchip Technologys PIC16F677 är en 8-bitars microcontroller som är användbar i många inbäddade konstruktioner. Den implementerar en synkron seriell port som kan styras för att kommunicera med det seriella perifera gränssnittet (SPI) eller I2C på andra styrenheter eller kringkretsar (figur 3).

Figur 3: PIC16F677 från Microchip Technology är en 8-bitars microcontroller som innehåller en synkron seriell port (med orange kontur) som kan programmeras som antingen en SPI- eller en I2C-buss. (Bildkälla: Microchip Technology)

Figur 3: PIC16F677 från Microchip Technology är en 8-bitars microcontroller som innehåller en synkron seriell port (med orange kontur) som kan programmeras som antingen en SPI- eller en I2C-buss. (Bildkälla: Microchip Technology)

Microcontrollern stöder både master- och slavläge för I2C med 7- eller 10-bitars adressering. Den använder SCK-/SCL-stiftet för I2C SCL-klocksignalen och SDI-/SDA-stiftet för datasignalen.

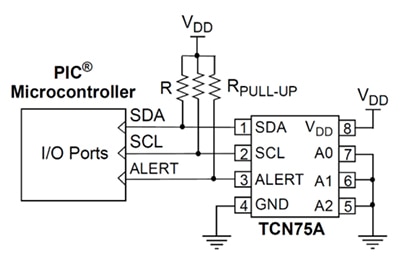

Dessa två stift ansluts till SCL- och SDA-ledningarna på I2C-bussen för att kunna kommunicera med andra enheter. En vanlig anslutning är till en I2C-baserad sensor som den seriella temperatursensorn med två ledningar från Microchip Technology, TCN75AVOA713 (figur 4).

Figur 4: Temperatursensorn TCN75A från Microchip Technology ansluts direkt till PIC16F677-microcontrollern för att kommunicera temperaturdata. (Bildkälla: Microchip Technology)

Figur 4: Temperatursensorn TCN75A från Microchip Technology ansluts direkt till PIC16F677-microcontrollern för att kommunicera temperaturdata. (Bildkälla: Microchip Technology)

Temperatursensorn har utökade funktioner, med funktioner för seriell kommunikation. De interna registren, som kan programmeras av användaren, kan användas till att sätta mätupplösning för temperatur, gå in i energisnålt avstängningsläge och t.o.m. sätta varningsutgången till att indikera när temperaturintervallet överskrider förinställda gränser.

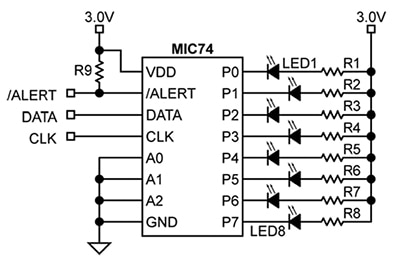

Det finns även ett antal enheter som avkodar den seriella I2C-dataströmmen och bryter ut den i parallell data. Överväg Microchip Technologys I/O-expander med två ledningar MIC74YQS-TR fläktenhet (figur 5).

Figur 5: I/O-expandern MIC74YQS-TR från Microchip Technology omvandlar den seriella standarddataströmmen i åtta separata parallella I/O-ledningar. (Bildkälla: Microchip Technology)

Figur 5: I/O-expandern MIC74YQS-TR från Microchip Technology omvandlar den seriella standarddataströmmen i åtta separata parallella I/O-ledningar. (Bildkälla: Microchip Technology)

Den här integrerade kretsen är en helt programmerbar I/O-expander med åtta separata I/O-ledningar. I/O-ledningarna kan programmeras individuellt som ingång eller utgång. Figur 5 visar MIC74YQS-TR som driver 8 lysdioder med styrning via en seriell buss. Det här liknar användningen av MCO23008 på I2C-demokortet i figur 1. MIC74YQS-TR kan, tillsammans med en spänningsregulator, också implementera en fläktmotorhastighetsstyrning med hjälp av sina fyra mest signifikanta bitar.

SMBus och I2C

Den seriella ingången till I/O-expandern är utformad för SMBus men är även kompatibel med I2C-bussen. SMBus-specifikationen är baserad på I2C och definierades av Intel och Duracell i 1994. Huvudskillnaden är att logiknivåerna för I2C i standardläge är relativa till VDD och nivåerna för SMBus är fasta. Det har visat sig i det flesta fall att det här inte är ett problem med VDD mellan 3 och 5 volt.

En annan skillnad är att SMBus är begränsad till klockfrekvenser på 100 kHz eller mindre, medan I2C har flera lägen som stöder högre klockfrekvenser. När det gäller busskompatibilitet begränsar det här den maximala klockfrekvensen till 100 kHz eller I2C-standardklockläget.

Så förutom i mycket speciella situationer är SMBus och I2C kompatibla.

Sammanfattning

I2C-bussen och enheter som bygger på den används i hundratals olika integrerade kretsar av alla möjliga typer, vilket gör det enkelt att ansluta dem i mångfacetterade konstruktioner och tillämpningar. Genom att koppla ihop blandsignalsensorer och analoga sensorer, kan användningsområdet för inbäddade microcontrollersystem utökas. Allt det här via ett enkelt seriellt digitalt gränssnitt med två ledningar.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.