Använd ett snabbspår med FPGA för att bygga högpresterande och strömsnåla Edge AI-applikationer

Bidraget med av DigiKeys nordamerikanska redaktörer

2021-01-12

Konstruktörer som vill implementera AI-algoritmer (artificiell intelligens) på inferensprocessorer i molnkanten är under konstant press att sänka strömförbrukningen och utvecklingstiden, även om kraven på processning ökar. Fältprogrammerbara grindmatriser (FPGA) erbjuder en särskilt effektiv kombination av hastighet och effektivitet för att implementera de inferensmotorer med neurala nätverk (NN) som krävs för Edge AI. För utvecklare som inte känner till FPGA kan konventionella FPGA-utvecklingsmetoder dock verka komplexa, vilket ofta får utvecklare att vända sig till mindre optimala lösningar.

Denna artikel beskriver en enklare metodik från Microchip Technology som gör det möjligt för utvecklare att undvika traditionell FPGA-utveckling, och istället bygga tränade neurala nätverk med hjälp av FPGA och ett programutvecklingsverktyg, eller använda ett FPGA-baserat videopaket för att omedelbart börja med smart inbäddad applikationsutveckling för maskinsyn.

Varför använda AI vid molnkanten?

Edge computing ger ett antal fördelar för IoT-applikationer i så olika segment som industriell automation, säkerhetssystem, smarta hem m.m. I en Industrial IoT-applikation (IIoT) som riktar sig mot fabriksgolv, kan processning i molnkanten dramatiskt förbättra responstiden i processtyrloopar med molnbaserade applikationer, eftersom datans "tur-och-retur"-resa kan elimineras. På samma sätt kan ett molnkantbaserat säkerhetssystem eller smarta dörrlås fortsätta att fungera även när anslutningen till molnet oavsiktligt eller avsiktligt avbryts. I många fall kan processning i molkanten i dessa tillämpningar bidra till att sänka de totala driftskostnaderna genom att minska produktens beroende av molnresurser. Istället för att konfronteras med ett plötsligt behov av mer av dyra molnresurser när efterfrågan på deras produkter ökar, kan utvecklare använda lokala processfunktioner som är inbyggda i produkterna för att bibehålla mer stabila driftskostnader.

Den snabba acceptansen och ökade efterfrågan på maskininlärningsmodeller (ML) förstärker dramatiskt vikten av processning i molnkanten. För utvecklare kan lokal processning av inferensmodeller bidra till att minska responstiden och kostnaderna för molnresurser som krävs för molnbaserad inferensering. För användarna skapar användning av lokala inferensmodeller förtroende för att deras produkter kommer att fortsätta fungera trots tillfälliga avbrott i internetanslutningen eller förändringar i produktleverantörens utbud av molnprodukter. Dessutom kan oro över säkerhet och integritet ytterligare leda till behov av lokal processning och inferensering för att begränsa mängden känslig information som överförs till molnet via det offentliga Internet.

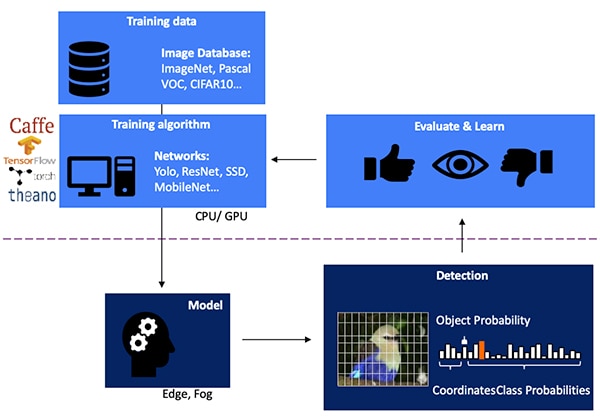

Att utveckla en NN-inferensmodell för visionsbaserad objektdetektering är en flerstegsprocess som börjar med modellträning, vanligtvis utförd på ett ML-ramverk som TensorFlow med offentligt tillgängliga etiketterade bilder eller anpassade bilder. På grund av processningskraven utförs modellträning vanligtvis med grafikprocessorer (GPU) i molnet eller en annan processorplattform med hög prestanda. När träningen är slutförd omvandlas modellen till en inferensmodell som kan köras på molnkant- eller hybridresurser och leverera inferensresultaten som en uppsättning sannolikheter för objektsklasser (Figur 1).

Figur 1: Implementering av en slutsatsmodell för AI i molnkanten ligger i slutet av en flerstegsprocess som kräver träning och optimering av NN i ramverk med hjälp av tillgänglig eller anpassad träningsdata. (Bildkälla: Microchip Technology)

Figur 1: Implementering av en slutsatsmodell för AI i molnkanten ligger i slutet av en flerstegsprocess som kräver träning och optimering av NN i ramverk med hjälp av tillgänglig eller anpassad träningsdata. (Bildkälla: Microchip Technology)

Varför slutsatsmodeller är beräkningsmässigt utmanande

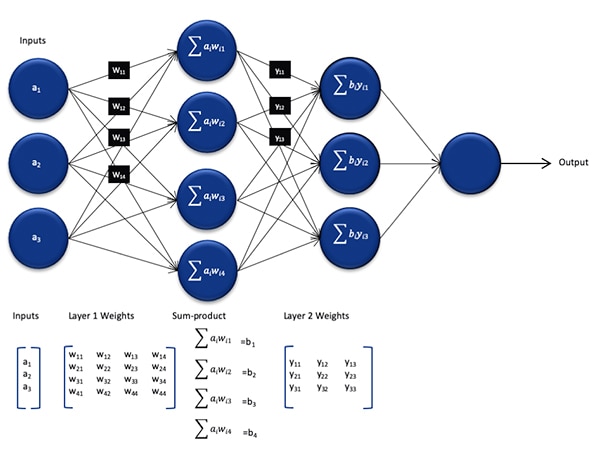

Även om den minskar i storlek och komplexitet jämfört med modellen som används under träningsprocessen, utgör en NN-inferensmodell fortfarande en beräkningsutmaning för konventionella processorer på grund av det stora antalet beräkningar som krävs. I sin generiska form omfattar en djup NN-modell flera lager av neuronuppsättningar. I varje lager i ett helt anslutet nätverk, behöver varje neuron nij beräkna summan av produkterna för varje ingång med tillhörande viktning wij (Figur 2).

Figur 2: Antalet beräkningar som krävs för inferensering med ett NN kan medföra en betydande beräkningsbelastning. (Bildkälla: Microchip Technology)

Figur 2: Antalet beräkningar som krävs för inferensering med ett NN kan medföra en betydande beräkningsbelastning. (Bildkälla: Microchip Technology)

I figur 2 visas inte de ytterligare beräkningskrav som ställs av aktiveringsfunktionen som modifierar utdatan från varje neuron genom att mappa negativa värden till noll, mappningsvärden större än 1 till 1 och liknande funktioner. Utgången från aktiveringsfunktionen för varje neuron nij fungerar som ingång till nästa lager i+1, och fortsätter på detta sätt för varje lager. Slutligen producerar utgångslagret i NN-modellen en utgångsvektor som representerar sannolikheten att den ursprungliga ingångsvektorn (eller matrisen) motsvarar en av de klasser (eller etiketter) som används under den övervakade inlärningsprocessen.

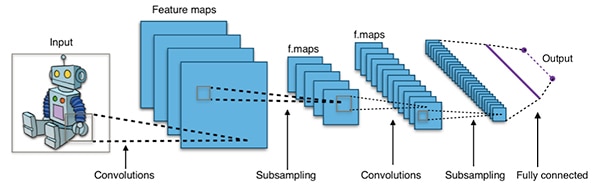

Effektiva NN-modeller är byggda med arkitekturer som är mycket större och mer komplexa än den representativa generiska NN-arkitekturen som visas ovan. Exempelvis tillämpar ett typiskt konvolutionellt NN (CNN) som används för detektering av bildobjekt dessa principer styckevis och scannar av bredden, höjden och färgdjupet hos en ingångsbild för att producera en serie funktionskartor som slutligen resulterar i förutsägelsevektorn (Figur 3).

Figur 3: CNN som används för detektering av bildobjekt involverar ett stort antal neuroner i många lager, vilket ställer större krav på processorplattformen. (Bildkälla: Aphex34 CC BY-SA 4.0)

Figur 3: CNN som används för detektering av bildobjekt involverar ett stort antal neuroner i många lager, vilket ställer större krav på processorplattformen. (Bildkälla: Aphex34 CC BY-SA 4.0)

Använda FPGA:er för att påskynda NN-matematik

Även om ett antal alternativ fortsätter att dyka upp för att köra inferensmodeller vid molnkanten, finns få alternativ för att få en optimal blandning av den flexibilitet, prestanda och effektivitet som behövs för praktisk höghastighetsinferensering vid molnkanten. Bland de lättillgängliga alternativen för AI i molnkanten är FPGA:er särskilt effektiva, eftersom de kan ge hårdvarubaserad högprestandaexekvering av beräkningsintensiva operationer samtidigt som de förbrukar relativt lite ström.

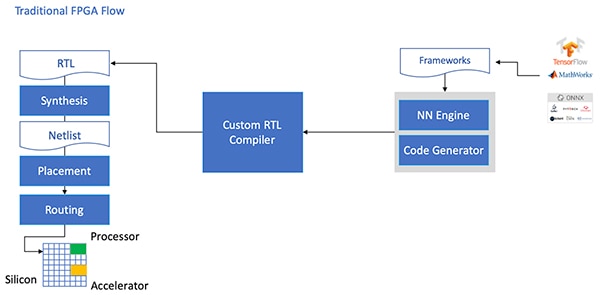

Trots deras fördelar förbises ibland FPGA:er till följd av ett traditionellt utvecklingsflöde som kan vara skrämmande för utvecklare utan solid FPGA-erfarenhet. För att skapa en effektiv FPGA-implementering av en NN-modell som genererats av ett NN-ramverk, behöver utvecklaren förstå nyanserna i att konvertera modellen till registeröverföringsspråk (RTL), syntetisera konstruktionen och arbeta igenom det slutliga fysiska designsteget för placering och hopkoppling, för att producera en optimerad implementation (Figur 4).

Figur 4: För att implementera en NN-modell på en FPGA, har utvecklare hittills behövt förstå hur man konverterar sina modeller till RTL och arbetar igenom det traditionella FPGA-flödet. (Bildkälla: Microchip Technology)

Figur 4: För att implementera en NN-modell på en FPGA, har utvecklare hittills behövt förstå hur man konverterar sina modeller till RTL och arbetar igenom det traditionella FPGA-flödet. (Bildkälla: Microchip Technology)

Med sina PolarFire-FPGA:er, specialiserad programvara och tillhörande immateriell egendom (IP), erbjuder Microchip Technology en lösning som gör högpresterande, strömsnål inferens vid molnkanten tillgängligt för utvecklare utan FPGA-erfarenhet.

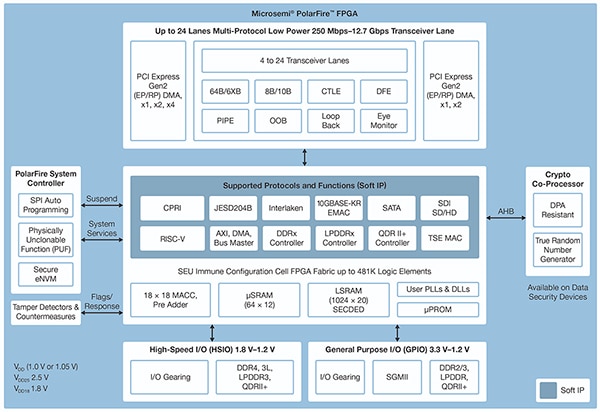

PolarFire-FPGA:erna är tillverkade i en avancerad icke-flyktig processteknik och är utformade för att maximera flexibiliteten och prestandan samtidigt som energiförbrukningen minimeras. Tillsammans med ett omfattande utbud av höghastighetsgränssnitt för kommunikation och input/output (I/O), har de ett djupt FPGA-struktur som kan bära upp avancerad funktionalitet med hjälp av mjuka IP-kärnor, inklusive RISC-V-processorer, avancerad minnesstyrning och andra standardiserade gränssnittsundersystem (Figur 5).

Figur 5: Microchip Technologys PolarFire-arkitektur erbjuder en djup struktur som är utformad för att klara höga konstruktionskrav på prestanda, som exempelvis beräkningskrävande inferensmodellimplementering. (Bildkälla: Microchip Technology)

Figur 5: Microchip Technologys PolarFire-arkitektur erbjuder en djup struktur som är utformad för att klara höga konstruktionskrav på prestanda, som exempelvis beräkningskrävande inferensmodellimplementering. (Bildkälla: Microchip Technology)

PolarFires FPGA-struktur ger en omfattande uppsättning logiska element och specialblock, vilka stöds för en rad olika kapaciteter av olika medlemmar i PolarFire FPGA-familjen, inklusive MPF100T, MPF200T, MPF300T och MPF500T serie (Tabell 1).

|

Tabell 1: En mängd olika FPGA-strukturfunktioner och kapaciteter är samlade i PolarFire-serien. (Tabellkälla: DigiKey, baserat på Microchip Technologys PolarFire-datablad)

Bland de särskilt intressanta funktionerna för inferensacceleration finns i PolarFire-arkitekturen ett dedikerat matematikblock som ger en 18×18-bitars signerad multiply-accumulate-funktion (MAC) med en föradderare. Ett inbyggt skalärproduktläge använder ett matematikblock för att utföra två 8-bitars multiplikationsoperationer, vilket ger en mekanism för att öka kapaciteten genom att dra nytta av den försumbara inverkan av modellkvantiseringen på noggrannheten.

Utöver att snabba upp de matematiska operationerna, bidrar PolarFire-arkitekturen till att avlasta den typ av minnesbelastning som påträffas vid implementering av inferensmodeller på konventionella arkitekturer, exempelvis små distribuerade minnen för lagring av mellanresultat som skapas under NN-algoritmkörning. En NN-modells vikter och biasvärden kan också lagras i ett 16 lager djupt gånger 18 bitars koefficient-ROM byggt från logiska element som ligger nära matematikblocket.

I kombination med andra PolarFire FPGA-strukturfunktioner ger matematikblock grunden för Microchip Technologys CoreVectorBlox IP för högre nivåer. Detta fungerar som en flexibel NN-motor som kan exekvera olika typer av NN. Utöver en uppsättning kontrollregister innehåller CoreVectorBlox IP tre viktiga funktionsblock:

- Microcontroller: En enkel mjuk RISC-V-processor som läser in det binära stora objektet (BLOB) i Microchips firmware och användarens specifika NN BLOB-fil från extern lagring. Den styr de övergripande CoreVectorBlox-operationerna genom att utföra instruktioner från firmwarens BLOB.

- Matrisprocessor (MXP): En mjukprocessor som består av åtta 32-bitars aritmetiska logikenheter (ALU) och är utformad för att utföra parallella operationer på datavektorer med elementvisa tensoroperationer, inklusive add, sub, xor, shift, mul, dotprod och andra, med blandad 8-, 16- eller 32-bitarsprecision efter behov.

- CNN-accelerator: Påskyndar MXP-operationer med en tvådimensionell array av MAC-funktioner som implementeras med hjälp av matematikblock och som körs med 8-bitarsprecision.

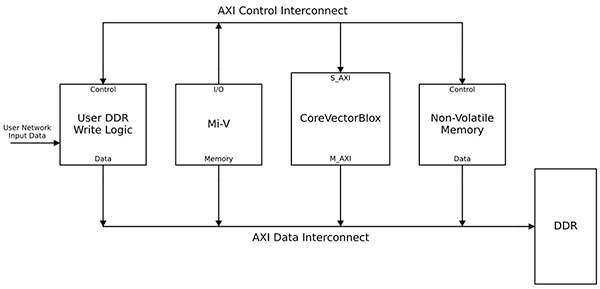

Ett komplett NN-processningssystem kombinerar ett CoreVectorBlox IP-block, minne, minneskontroll och en värdprocessor, såsom mjukvaruprocessorkärnan Microsoft RISC-V (Mi-V) (Figur 6).

Figur 6: CoreVectorBlox IP-blocket körs med en värdprocessor som Microchips Mi-V RISC-V-microcontroller för att implementera en NN-inferensmodell. (Bildkälla: Microchip Technology)

Figur 6: CoreVectorBlox IP-blocket körs med en värdprocessor som Microchips Mi-V RISC-V-microcontroller för att implementera en NN-inferensmodell. (Bildkälla: Microchip Technology)

I en videosystemimplementering kommer värdprocessorn att ladda firmwaren och nätverks-BLOB från systemminnet och kopiera dem till DDR RAM-minnet för användning av CoreVectorBlox-blocket. När videorutor anländer, skriver värdprocessorn in dem i DDR RAM-minnet och signalerar till CoreVectorBlox-blocket att börja bearbeta bilden. Efter att den kört inferensmodellen som definierats i nätverkets BLOB, skriver CoreVectorBlox-blocket resultaten, inklusive bildklassificering, tillbaka till DDR RAM-minnet för användning av målapplikationen.

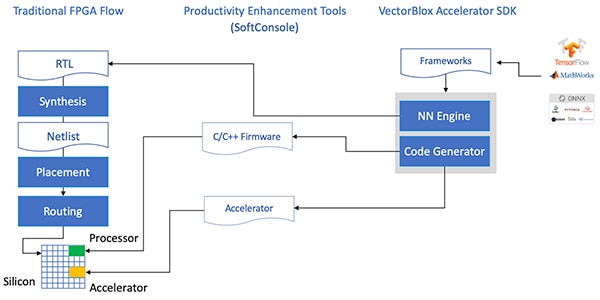

Utvecklingsflödet förenklar NN FPGA-implementering

Microchip skyddar utvecklare från komplexiteten i att implementera en NN-inferensmodell på PolarFire-FPGA:er. Istället för att hantera detaljerna i det traditionella FPGA-flödet arbetar NN-modellutvecklare som vanligt med sina NN-ramverk och läser in den resulterande modellen i Microchip Technologys VectorBlox Accelerator Software Development Kit (SDK). SDK:et genererar den nödvändiga uppsättningen filer inklusive de som behövs för det normala FPGA-utvecklingsflödet och de fasta programvaru- och nätverks-BLOB-filerna som nämnts tidigare (Figur 7).

Figur 7: VectorBlox Accelerator SDK hanterar detaljerna i att implementera en NN-modell på en FPGA och genererar automatiskt filer som behövs för att konstruera och köra den FPGA-baserade inferensmodellen. (Bildkälla: Microchip Technology)

Figur 7: VectorBlox Accelerator SDK hanterar detaljerna i att implementera en NN-modell på en FPGA och genererar automatiskt filer som behövs för att konstruera och köra den FPGA-baserade inferensmodellen. (Bildkälla: Microchip Technology)

Eftersom VectorBlox Accelerator SDK-flödet överlagras NN-designen på NN-motorn som implementerats i FPGA:n, kan olika NN köras på samma FPGA-design utan att behöva göra om FPGA-designsyntesflödet. Utvecklare skapar kod i C/C++ för det resulterande systemet och kan växla modeller i systemet direkt eller köra modeller samtidigt med tidsmultiplexing.

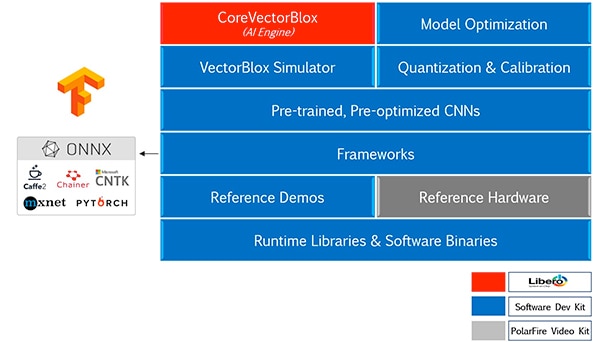

VectorBlox Accelerator SDK kombinerar Microchip Technologys Libero FPGA-utvecklingssvit med en stor uppsättning funktioner för utveckling av NN-inferensmodeller. Utöver modelloptimerings-, kvantiserings- och kalibreringstjänster tillhandahåller SDK:et även en NN-simulator som låter utvecklare använda samma BLOB-filer för att utvärdera sin modell innan de används i FPGA-hårdvaruimplementeringen (Figur 8).

Figur 8: VectorBlox Accelerator SDK tillhandahåller en omfattande uppsättning tjänster som är utformade för att optimera FPGA-implementering av ramgenererade inferensmodeller. (Bildkälla: Microchip Technology)

Figur 8: VectorBlox Accelerator SDK tillhandahåller en omfattande uppsättning tjänster som är utformade för att optimera FPGA-implementering av ramgenererade inferensmodeller. (Bildkälla: Microchip Technology)

VectorBlox Accelerator SDK:et stöder modeller i Open Neural Network Exchange (ONNX)-format samt modeller från ett antal ramverk som TensorFlow, Caffe, Chainer, PyTorch och MXNET. CNN-arkitekturer som stöds inkluderar MNIST, MobileNet-versioner, ResNet-50, Tiny Yolo V2 och Tiny Yolo V3. Microchip arbetar för att utöka stödet till att omfatta de flesta nätverken i OpenVINO toolkit Open Model Zoo med förtränade open-source-modeller, inklusive Yolo V3, Yolo V4, RetinaNet och SSD-MobileNet bland många andra.

Videokit demonstrerar FPGA-inferens

För att hjälpa utvecklare att snabbt komma igång med smart inbäddad applikationsutveckling för maskinsyn, erbjuder Microchip Technology en omfattande testapplikation som är utformad för att köras på företagets MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit and reference design.

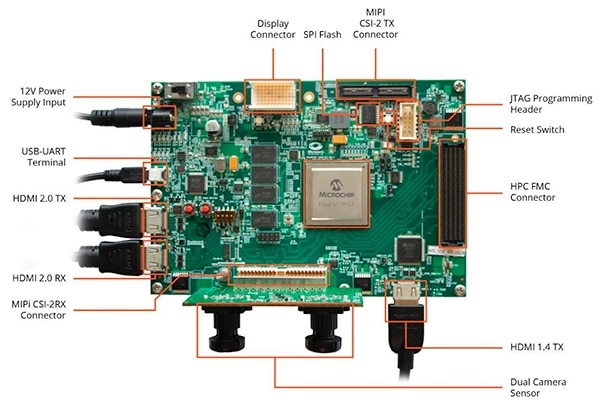

Baserat på Microchips MPF300T PolarFire FPGA kombinerar satsens kort en dubbel kamerasensor, dubbel datahastighet 4 (DDR4) RAM, flashminne, strömhantering och en mängd olika gränssnitt (Figur 9).

Bild 9: MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit och tillhörande programvara ger utvecklare en snabb start till FPGA-baserad inferens i smarta inbäddade maskinsynsapplikationer. (Bildkälla: Microchip Technology)

Bild 9: MPF300-VIDEO-KIT PolarFire FPGA Video and Imaging Kit och tillhörande programvara ger utvecklare en snabb start till FPGA-baserad inferens i smarta inbäddade maskinsynsapplikationer. (Bildkälla: Microchip Technology)

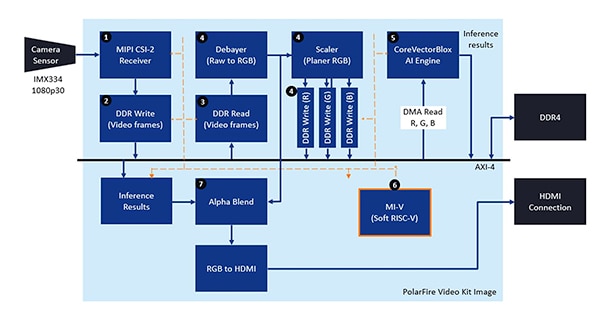

Paketet levereras med ett komplett Libero-designprojekt som används för att generera BLOB-filer för firmware och nätverk. När utvecklarna har programmerat BLOB-filerna till det inbyggda flashminnet kan de klicka på run-knappen i Libero för att starta demonstrationen som processar videobilder från kamerasensorn och visar slutresultat på en bildskärm (Figur 10).

Figur 10: Microchip Technologys PolarFire FPGA Video and Imaging Kit visar hur man konstruerar och använder en FPGA-implementering av ett smart inbäddat maskinsynssystem byggt kring Microchip CoreVectorBlox NN-motorn. (Bildkälla: Microchip Technology)

Figur 10: Microchip Technologys PolarFire FPGA Video and Imaging Kit visar hur man konstruerar och använder en FPGA-implementering av ett smart inbäddat maskinsynssystem byggt kring Microchip CoreVectorBlox NN-motorn. (Bildkälla: Microchip Technology)

För varje inmatad videoruta utför det FPGA-baserade systemet följande steg (med stegnummer som korrelerar till figur 10):

- Ladda en ruta från kameran

- Lagra rutan i RAM-minnet

- Läs rutan från RAM-minnet

- Konvertera den råa bilden till RGB och planar RGB och lagrar resultatet i RAM-minnet

- Mi-V soft RISC-V-processorn startar CoreVectorBlox-motorn, som hämtar bilden från RAM, utför inferens och lagrar resultaten från klassificeringssannolikheten tillbaka till RAM-minnet

- Mi-V använder resultaten för att skapa en överläggsruta med avgränsande rutor, klassificeringsresultat och andra metadata och lagrar rutan i RAM-minnet

- Originalrutan blandas med överläggsrutan och skrivs till HDMI-skärmen

Demonstrationen stöder acceleration av Tiny Yolo V3 och MobileNet V2-modeller, men utvecklare kan köra andra SDK-stödda modeller med de metoder som beskrivits tidigare genom att göra en liten kodändring för att lägga till modellnamn och metadata till den befintliga listan som innehåller de två standardmodellerna.

Slutsats

AI-algoritmer som NN-modeller påför vanligtvis beräkningsintensiva arbetsbelastningar som kräver mer robusta datorresurser än som är tillgängligt med konventionella processorer. Även om FPGA-enheter är väl rustade för att uppfylla kraven på prestanda och strömsnålhet för att exekvera inferensmodeller, kan konventionella FPGA-utvecklingsmetoder upplevas som komplexa, vilket ofta får utvecklare att vända sig till suboptimala lösningar.

Som vi sett kan utvecklare utan FPGA-erfarenhet, med hjälp av specialiserad IP och programvara från Microchip Technology, implementera inferensbaserade konstruktioner som bättre uppfyller kraven på prestanda, strömsnålhet och designplanering.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.