Använd en effektiv flerkärnig processor för att bygga smartare röstaktiverade produkter

Bidraget med av DigiKeys nordamerikanska redaktörer

2020-02-14

Efterfrågan på smartare produkter är stor i nästan alla tillämpningsområden eftersom användarna blivit bekanta med och förlitar sig på virtuella digitala assistenter som Amazon Alexa, Google Assistant, Apple Siri, Microsoft Cortana med flera. Förutom att de är praktiska spelar dessa assistenter en allt större roll i att förbättra säkerheten i ett stort urval produkter för industriella system och vårdtillämpningar. För utvecklare innebär de underliggande konstruktionerna för dessa produkter ibland motstridiga krav för processorer som kan leverera ökad prestanda, optimerad kostnad och fysiskt format och effektiv drift.

Den här artikeln visar hur utvecklarna kan använda en flerkärnig processor – i det här fallet i.MX 8M Nano från NXP – för att uppfylla de kraftigt varierande behandlings- och gränssnittskraven för framväxande smarta produkter i tillämpningssegment från smarta hem och industriautomatisering till medicinska system. Framförallt visar den här artikeln hur utvecklarna kan använda den här processorn för att enklare implementera nästa generations röstbaserade lösningar med avancerade ljudbehandlingsfunktioner.

Hur smarta produkter utvecklas

Den snabba framväxten av röstassistenttekniker har fått användarna att leta efter mer funktion från smarta produkter. Kommande produkter behöver inte bara svara på röstkommandon utan behöver även bädda in mer smart teknik som använder en större variation i ingångsdata från sensorer, kameror och andra produkter. Det räcker inte att smarta ljusströmställare kan slå på och stänga av ljuset eller att diskmaskiner reagerar på röstkommandon. I takt med att tillämpningarna blir mer sofistikerade, måste deras underliggande enheter ha stöd för mer varierande kombinationer av sensorer, förbättrad behandlingskapacitet med artificiell intelligens (AI) och 3D-grafikdisplayer.

Behovet av smartare produkter sträcker sig bortom önskemål om större användarvänlighet. I kritiska tillämpningar som industriautomation och sjukvård kan det vara viktigt att enheter kan varna användarna om faror eller sjukdomstillstånd i förebyggande syfte. En fabriksarbetare som använder en hjälm som kan övervaka den omedelbara omgivningen kan enklare undvika risker, och en patient som har på sig en liten hälsoövervakningsenhet som kontinuerligt övervakar vitala funktioner kan få nödvändig behandling innan en krissituation uppstår.

Dessa och andra smarta produkter medför specifika designkrav som varierar lika mycket som de tänkta tillämpningarna, men de flesta har behov av processning med hög prestanda, multimediafunktioner och säker drift. För utvecklare kombineras dessa funktionskrav med det fundamentala behovet av lösningar som kan skalas upp för att hantera mer robusta tillämpningar, samtidigt som lösningarna måste skalas ner fysiskt för att uppfylla användarnas förväntningar på minskad storlek, lägre kostnad och minskad strömförbrukning. Processorfamiljen NXP i.MX 8M Nano bygger på en heterogen flerkärnearkitektur och uppfyller de varierande kraven på konstruktioner för kommande smarta produkter.

Kärnor med hög prestanda

NXP i.MX 8M Nano är den senaste medlemmen i processorfamiljen NXP i.MX 8M och är utformad för att tillhandahålla en skalbar flerkärnig behandlingsplattform. För avancerade videotillämpningar finns NXP i.MX 8M:s topprocessorer som MIMX8MQ5DVAJZAB som ger upp till 4K skärmupplösning med hårdvaruavkodning av 4K HDR-video. För 1080p-video ger NXP i.MX 8M Mini-processorerna som MIMX8MM6CVTKZAA 1080p hårdvaruavkodningsstöd. Både i.MX 8M- och 8M Mini-serien kombinerar upp till fyra Arm® Cortex®-A53-processorkärnor med en Arm Cortex-M4F-microcontrollerkärna.

Till skillnad från dessa kombinerar NXP i.MX 8M Nano MIMX8MN6CVTIZAA-processorn fyra Arm Cortex-A53-kärnor med en Arm Cortex-M7-kärna som ger den den högsta prestandan av kärnorna i Arm Cortex-M-serien, inklusive Cortex-M4F.

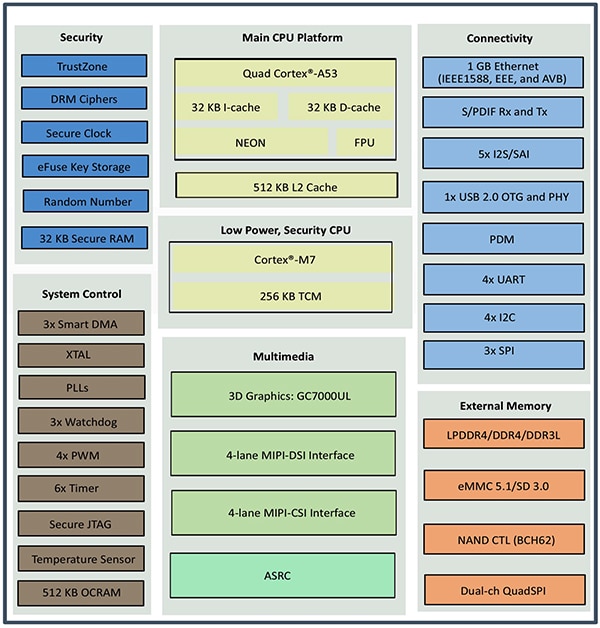

Utöver sin bestyckning av processorkärnor, har i.MX 8M Nano-processorerna stöd för ett stort urval av externa minnesenheter och tillhandahåller ett stort sortiment av externa kringenhetsgränssnitt som normalt krävs i konsument- och industritilllämpningar (figur 1).

Figur 1: NXP i.MX 8M Nano-processorn kombinerar upp till fyra Arm Cortex-A53-tillämpningsprocessorer, en Arm Cortex-M7-microcontroller, specialiserade hårdvarusubsystem med omfattande externa kringutrustningsgränssnitt som normalt används i konsument- och industritillämpningar. (Bildkälla: NXP)

Figur 1: NXP i.MX 8M Nano-processorn kombinerar upp till fyra Arm Cortex-A53-tillämpningsprocessorer, en Arm Cortex-M7-microcontroller, specialiserade hårdvarusubsystem med omfattande externa kringutrustningsgränssnitt som normalt används i konsument- och industritillämpningar. (Bildkälla: NXP)

De olika tillgängliga varianterna av i.MX 8M Nano-processorserien gör att utvecklarna enkelt kan uppfylla sina specifika krav när det gäller kostnad och prestanda. Till exempel har högprestandaenheterna ett omfattande utbud av specialiserade subsystem för säkerhet, 3D-grafikdisplayer, ljudbehandling med mera. Andra medlemmar i i.MX 8M Nano-serien erbjuder alternativ med färre Cortex-A53-kärnor och Lite-versioner med minskade grafikegenskaper.

Alla medlemmar i i.MX 8M Nano-processorserien levererar dock den kombination av tillämpningsprestanda och realtidskapacitet som krävs i moderna smarta produkter.

Arm Cortex-A53-processorkärnorna är utformade för att köra programvara med hög prestanda och kan ge arbeta på klockfrekvenser upp till 1,5 GHz samtidigt som de arbetar från dedikeran nivå 1 (L1) 32 kbyte instruktionscache (I-cache), 32 kbyte datacache (D-cache), och ett delat L2 förenat cache på 512 kbyte. Tillsammans med sin integrerade flyttalsprocessor (FPU) ger dessa kärnor stöd för Arms Neon-teknik för avancerade SIMD-funktioner (single instruction multiple data) som används vid digital signalbehandling och andra avancerade algoritmer i dataintensiva tillämpningar.

För inbäddade systemkrav körs Arm Cortex-M7-microcontrollerkärnan vid frekvenser upp till 750 MHz samtidigt som den tillhandhåller körning med hög prestanda av realtidsprocesser som kräver låg latens och förutsägbar drift. För att påskynda processningen ytterligare inkluderar kärnan en integrerad FPU och 256 kbyte TCM-minne (tightly coupled memory) som används för instruktions- och datacache.

För komplexa processningsuppgifter i realtid kan dock förmågan att snabbt identifiera separata störningskällor vara lika kritiskt som rå processningskraft. I i.MX 8M Nano-processorerna möjliggör en GIC-enhet (global interrupt controller) som är inbyggd i varje Arm Cortex-A53-kärna och en NVIC-enhet (nested vector interrupt controller) i Arm Cortex-M7-kärnan finkornig störningshantering från närmare 128 distinkta källor för interruptbegäran som motsvarar kärnstatusar, timers, händelser i kringutrustningsgränssnitt, DMA-funktioner (direct-memory access), specialiserade hårdvaruprocesser med mera.

Heterogen flerkärnebearbetning

Varje i.MX 8M Nano-processorkärna tillhandahåller en robust beräkningsresurs separat. När de används tillsammans erbjuder processorns flera kärnor en kraftfull beräkningsplattform som kan hantera de konkurrerande kraven på realtidsprestanda och körning av programvara som kan försvåra utformningen av smarta produkter. En smart produkt som baseras på den här processorn kan till exempel använda Cortex-M7-kärnan för att bearbeta ljudströmmar i realtid och samtidigt använda algoritmer som körs på en eller flera Cortex-A53-kärnor för att analysera resulterande data och ge användarna en 3D-grafikavbildning av resultaten.

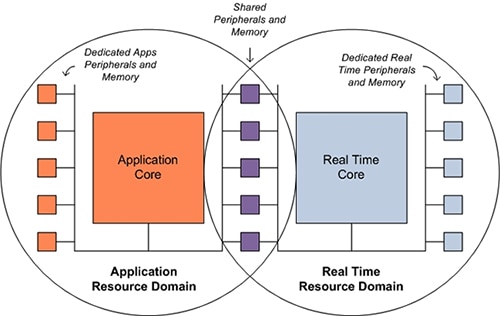

För att utföra den här typen av koordinerad, heterogen flerkärnebearbetning tillförlitligt, kräver dock ett flerkärnesystem noggrann anordning av bearbetningsfunktionerna och datautbytet mellan de olika kärnorna, specialiserade hårdvarublocken och kringkretsarna. I i.MX 8M Nano-processorn är den här organiseringen inbyggd i hårdvarubaserade mekanismer för semaforer och meddelandefunktioner som typiskt sett används av programvarutjänster på låg nivå i multiprocessormiljöer.

I inbäddade system utökas den här organiserade körningen även till hårvaruresurser som minne och kringkretsar. För den här uppgiften innehåller processorn en dedikerad resursdomäncontroller (RDC) som är utformad för att säkerställa säker resursdelning, eller tillförlitlig isolation där det krävs. Som en följd av detta kan tillämpningsprogramvara och realtidskod styra resurser som är dedikerade till domänen, samtidigt som de delar en uppsättning gemensamma resurser (figur 2).

Figur 2: Hårvarubaserade mekanismer i NXP i.MX 8M Nano-processorn säkerställer isolation av resurser som är dedikerade till Cortex-A53-tillämpningsdomänen eller Cortex-M7-realtidsdomänen samtidigt som säker resursdelning möjliggörs vid behov. (Bildkälla: NXP)

Figur 2: Hårvarubaserade mekanismer i NXP i.MX 8M Nano-processorn säkerställer isolation av resurser som är dedikerade till Cortex-A53-tillämpningsdomänen eller Cortex-M7-realtidsdomänen samtidigt som säker resursdelning möjliggörs vid behov. (Bildkälla: NXP)

Specialiserat stöd för smarta produkter

Med i.MX 8M Nano-processorns flera kärnor och resursdelningsfunktioner kan utvecklarna skapa sofistikerade tillämpningar för nya smarta produkter som byggs med röstassistenter och 3D-grafik. Dessa tillämpningar får en ytterligare prestandaförstärkning medan de minskar sitt programvaruberoende tack vara specialiserat hårdvarustöd för smarta produkter, som är inbyggt i i.MX 8M Nano-processorerna.

När det gäller grafik ger processorns integrerade grafikprocessor 2D- och 3D-grafikacceleration och stödjer standardgrafikbibliotek inklusive Vulkan, Open CL (Open Computing Language) och OpenGL (Open Graphics Library). En integrerad LCD-gränssnittsstyrenhet (LCDIF) har stöd för displayer med 1080p60 (1080 progressiv 60 bildrutor per sekund).

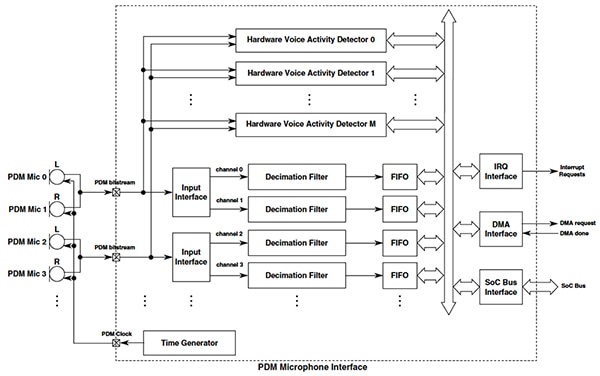

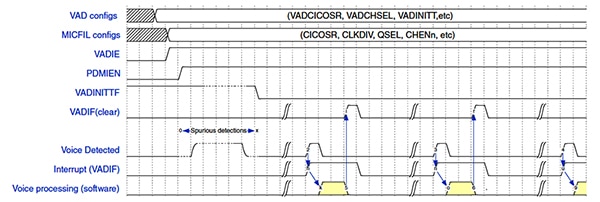

GPU:n i kretsen avlastar kärnorna genom att hantera displayprocessningen medan en annan uppsättning hårdvarusubsystem hanterar ett antal ljudbehandlingsuppgifter som normalt saktar ner system som bygger på konventionella processorer. För behandling av mikrofoningångar finns processorns pulstäthetsmoduleringsbaserade (PDM) mikrofongränssnitt (MICFIL) som erbjuder en flerstegspipeline som är utformad för att generera filtrerad 16-bitars pulskodsmodulerade (PCM) data från 1-bitarsinsignalerna från PDM-mikrofonerna (figur 3).

Figur 3: NXP i.MX 8M Nano-processorns gränssnittssubsystem för PDM-mikrofoningångar kombinerar separata hårvarupipelines för behandling av ljudsignaler och röstaktivitetsidentifiering. (Bildkälla: NXP)

Figur 3: NXP i.MX 8M Nano-processorns gränssnittssubsystem för PDM-mikrofoningångar kombinerar separata hårvarupipelines för behandling av ljudsignaler och röstaktivitetsidentifiering. (Bildkälla: NXP)

För en typisk röstbaserad tillämpning behöver konstruktörerna bara ansluta en PDM-mikrofon till en av de åtta PDM-kanalerna som stöds av processorn. I PDM-mikrofonens gränssnittssubsystem kombinerar ett ingångsgränssnitt tidsmultiplexerad PDM-data från ett par mikrofoner för att bilda en bana som består av den vänstra och högra kanalen.

I nästa steg för varje kanal ger ett dedikerat programmerbart dämpningsfilter olika genomsläppsband beroende på önskad utgångssignal och en av sex kvalitetsvalsinställningar (QSEL) inklusive hög, medelhög och låg kvalitet, samt tre ytterligare mycket låga kvalitetsnivåer. Till exempel: vid 48 kilohertz (kHz) utmatning ställer de lägsta kvalitetslägena in filtrets genomsläppsband på 10,5 Hz till 11,25 kHz jämfört med ett genomsläppsband på 21 Hz till 22,5 kHz för högt, medelhögt och lågt kvalitetsläge. Slutligen görs resultaten för varje kanal tillgängliga i separata FIFO-buffertar (first-in, first-out) för varje kanal för att generera interrupt, överföring med DMA eller bussåtkomst.

Hårdvarubaserad identifiering av röstaktiviteter

Tillsammans med den här konditioneringspipelinen för ljudsignaler erbjuder PDM-mikrofongränssnittet en uppsättning hårdvarubaserade identifierare av röstaktiviteter (HWVAD:er) som övervakar de önskade mikrofoningångskanalerna. (Obs! Figuren ovan anger att varje HWVAD är kopplad till en bana, men dokumentationen anger att kanaler, och namnet på ett register, VADCHSEL, stöder detta). För att ge stöd för HWVAD-funktion tillhandahåller processorn en stor uppsättning enhetsregister som gör det möjligt för utvecklarna att definiera den specifika HWVAD-konfiguration som krävs för deras tillämpning (tabell 1).

|

Tabell 1: NXP i.MX 8M Nano-processorregister används typiskt sett för att konfigurera hårdvarans röstaktivitetsdetektorer som integrerats i processorns PDM-mikrofongränssnitt (MICFIL). (Tabellkälla: DigiKey, baserad på NXP-data)

Utifrån dessa registerinställningar använder HWVAD inbyggda röstidentifieringsalgoritmer för att identifiera röstaktivitet. Vid identifiering genererar HWVAD ett avbrott för att aktivera en kärna, typiskt sett Cortex-M7, för ytterligare processning (figur 4).

Figur 4: Med konfigurationsinställningar som programmerats av utvecklaren tillåter NXP i.MX 8M Nano-processorns hårdvarubaserade röstaktivitetsdetektorer processorkärnorna att vila eller utföra annan processning tills en röst identifieras och ytterligare röstbehandling krävs. (Bildkälla: NXP)

Figur 4: Med konfigurationsinställningar som programmerats av utvecklaren tillåter NXP i.MX 8M Nano-processorns hårdvarubaserade röstaktivitetsdetektorer processorkärnorna att vila eller utföra annan processning tills en röst identifieras och ytterligare röstbehandling krävs. (Bildkälla: NXP)

I en röstassistenttillämpning söker kärnan igenom ljudströmmen för det aktuella aktiveringsordet. Om aktiveringsordet identifieras skickar kärnan typiskt sett ljudströmmen till de molnbaserade röstassistenttjänsterna som stöds av tillämpningen.

Utöver PDM-mikrofongränssnittets subsystem, erbjuder i.MX 8M Nano-processorn dessutom fem synkrona ljudgränssnittsmoduler (SAI) som har stöd för ett antal standardljudformat, inklusive Inter-IC Sound (I2S), ljudcodec 97 (AC97), TDM-ljud (time division multiplexed) och DSD (Direct Stream Digital) samt codec- eller digital signalbehandlingsdata (DSP).

För att uppfylla de specifika tillämpningskraven står utvecklarna ofta inför uppgiften att omvandla ingående ljudprov till någon annan samplingsfrekvens och upplösning. Istället för att använda processorcykler för denna uppgift innehåller i.MX 8M Nano-processorn ett dedikerat ASRC-subsystem (asynchronous sample rate converter).

ASRC har kapacitet för samtidig bearbetning av upp till 32 ljudkanaler och omvandlar automatiskt källsamplingar till önskad samplingsfrekvens (mellan 8 kHz och 384 kHz) och upplösning (IEEE single-precision floating point- eller fixed point-format med 16, 20, 24 eller 32 bitar per prov). Under processen omvandlar ASRC alla ingående data till 64-bitars IEEE flytande punkt-format för att säkerställa korrekt upp- eller nedomvandling av ljudsamplingsdata efter behov för att uppnå önskat resultat.

Krafthantering med en allmän kraftstyrenhet

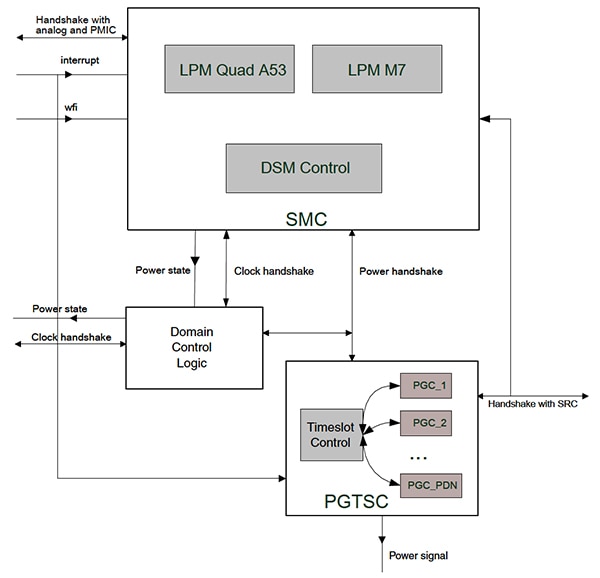

Med sin omfattande integrering av processorkärnor och hårdvarusubsystem kombinerar NXP i.MX 8M Nano-processorarkitekturen ett antal separata kraftdomäner och kraftlägen som är inbyggda i de enskilda kärnorna och subsystemen. För att hantera kraften för den här uppsättningen kärnor och specialiserade block, inkluderar i.MX 8M Nano-processorn en sofistikerad GPC-enhet (general power controller) som är utformad för att samordna flera krafthanteringsfunktioner. I GPC hanterar SMC-enheten (system mode controller) varje kärnas lågeffektläge (LPM) och övergripande DSM-läge (deep sleep mode), medan en PGTSC-enhet (power gating time slot controller) hanterar klockgrindningen som används för att minska systemeffekten genom att kapa strömmen till inaktiva subsystem (figur 5).

Figur 5: För att förbättra effektoptimeringen på systemnivå innehåller NXP i.MX 8M Nano en omfattande kraftstyrenhet som hanterar effektgrindningsfunktionerna och lågeffektlägena som är inbyggda i processorkärnorna. (Bildkälla: NXP)

Figur 5: För att förbättra effektoptimeringen på systemnivå innehåller NXP i.MX 8M Nano en omfattande kraftstyrenhet som hanterar effektgrindningsfunktionerna och lågeffektlägena som är inbyggda i processorkärnorna. (Bildkälla: NXP)

Under antingen programvaru- eller hårdvarukontroll, använder GPC 20 olika tidsluckor i PGTSC för att aktivera eller inaktivera någon av de många klockgrindade effektdomänerna i processorn. Här arbetar tidsluckstyrenheten i sekvens genom dessa tidsluckor och aktiverar eventuella aktiverings- eller inaktiveringsförfrågningar innan den går till nästa lucka. Utöver att uppfylla specifika effektsekvenskrav tillåter den här metoden att utvecklarna minskar upprampningsströmmen under systemstart eller när systemet väcks från lågeffektläge eller djupt viloläge.

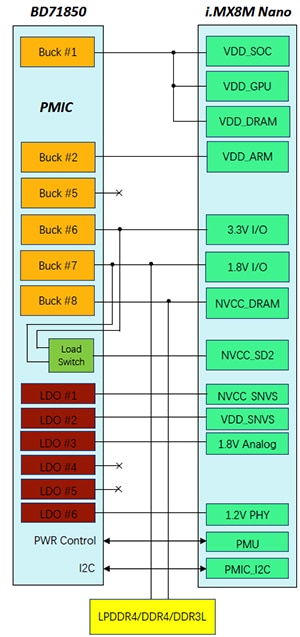

Det är enkelt att försörja i.MX 8M Nano-processorns flera effektdomäner. ROHM Semiconductors BD71850MWV-PMIC (power management integrated circuit) är särskilt utformad för att ge stöd åt NXP i.MX 8M Nano-processorn och erbjuder alla strömmatningar som processorn behöver samt övriga systemkringkretsar. BD71850MWV-PMIC:en innehåller en egen effektsekvenserare, vilket underlättar en säker start- och avstängningssekvens, inte bara för processorn utan även för externt minne, sensorer eller andra enheter i systemet (figur 6). Utvecklarna behöver inga extrakomponenter för att integrera BD71850MWV-PMIC:en i en konstruktion utöver de vanliga avkopplingskondensatorerna (visas inte).

Figur 6: NXP iMX 8M Nano-processorns flera kärnor och hårdvarusubsystem driver behovet av flera matningsskenor, men ROHM:s PMIC BD71850MWV innebär en färdig lösning. (Bildkälla: NXP)

Figur 6: NXP iMX 8M Nano-processorns flera kärnor och hårdvarusubsystem driver behovet av flera matningsskenor, men ROHM:s PMIC BD71850MWV innebär en färdig lösning. (Bildkälla: NXP)

Utvecklingsstöd

Trots att hårdvarugränssnittskraven för i.MX 8M Nano-baserade konstruktioner är relativt enkla innebär NXP att utvecklarna slipper även den här förhållandevis enkla konstruktionsuppgiften vid utvärdering av processorn eller prototypkonstruktion för nya smarta produkter. Med en helt implementerad utvecklingssats och referensdesign för i.MX 8M Nano-processorn, kombinerar 8MNANOD4-EVK-utvärderingssatsen i.MX 8M Nano-processorn och BD71850MWV-PMIC:en med Murata Electronics Wi-Fi/Bluetooth-sändtagarmodul LBEE5HY1MW, vilket sammantaget ger en plattform för omedelbar utvärdering och prototyputveckling. Utöver flera gränssnittsalternativ och förknippade kontaktdon innehåller utvärderingssatsen en full uppsättning av externa minnesenheter inklusive SDRAM (static dynamic ram), NOR flash och NAND flash. Med utvärderingssatsen kan utvecklarna utforska olika driftlägen och konfigurationer inklusive start från externt flash eller säker start med signerade startavbildningar.

När utvecklarna är klara att fortsätta med sin egen anpassade programvaruutveckling erbjuder NXP drivkretsar, kortstödpaket (BSP:er) och mellanprogramvara som är utformad för att köras med såväl sin egen MCUXpresso-integrerade utvecklingsmiljö (IDE), som IDE:er från tredje part. För att bygga tillämpningar som är utformade för att utnyttja maskininlärningsmetoder kan utvecklarna vända sig till NXP eIQ-utvecklingsmiljön för maskininlärningsprogramvara och i.MX-optimerade tolkningsbibliotek som eIQ för TensorFlow Lite för Cortex-M7-baserad tolkning eller NXP:s portering av Arms programvaruutvecklingssats för neurala nätverk (NN SDK) för Cortex-A53-baserad tolkning.

Slutsats

Genom den snabba acceptansen av röstassistentprodukter medför nästa generations smarta produkter växande förväntningar på inte bara bättre ljudstöd, utan även högre prestanda, förbättrad grafik och strömsnål drift. För utvecklarna kräver dock effektiv systemdesign för dessa produkter en kombination av programvarukörning med hög prestanda och realtidsfunktioner med låg latens, vilket har varit svårt att uppnå med de förknippade begränsningarna av storlek, kostnad och effekt. Genom tillgängligheten till en skalbar familj av flerkärniga processorer från NXP kan utvecklarna enkelt uppfylla designkraven på smarta produkter i en bred uppsättning tillämpningssegment, inklusive konsumentprodukter, industri och medicin, bland andra.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.