Använd en enskild HMP-processor med ultralåg effekt för arbetsbelastningar både i realtid och tillämpningsbehandling

Bidraget med av DigiKeys nordamerikanska redaktörer

2019-08-06

Konsumenter förväntar sig att personelektronik och andra mobila enheter ska ge snabbare respons och högre funktionalitet – samtidigt som batterilivslängden ska förbättras. För utvecklare har dock kraven för realtidssvar och höga prestanda i många tillämpningar dikterat användningen av separata processorer som ska hantera dessa motsatta krav. Detta ökar kostanden, effekt- och utrymmeskraven samt både maskinvarulayouten och programvarans komplexitet.

En bättre metod skulle vara att integrera den nödvändiga maskinvaran i ett enda chip. Ange heterogena enheter för flerkärnebearbetning (HMP). Dessa processorer innehåller flera kärnor av olika typer och kan erbjuda fördelar med prestandaoptimering, minskad effektförbrukning och förbättrad systemsäkerhet och tillförlitlighet.

Den här artikeln beskriver hur utvecklare kan använda en heterogen flerkärnig processor från NXP Semiconductors för att uppfylla efterfrågan på dessa blandade arbetsbelastningar utan att kompromissa med kraven på låg effekt och minskad designkomplexitet.

Ändrade krav.

Framsteg inom sensorteknik och databehandlingsalgoritmer har skapat stora möjligheter för utvecklare att hantera de konkurrerande kraven på datainsamling i realtid och körning av beräkningsintensiva algoritmer. Tidigare har utvecklarna normalt delat upp dessa arbetsbelastningar i separata system.

I nätverkshierarkins lägsta nivå brukade inbäddade processorer som modeller som byggde på Arm® Cortex®-M4-kärnan samla in data, köra optimerad kod i realtidsoperativsystem (RTOS) eller barmetallsystem. PÅ en högre nivå i hierarkin körde högpresterande tillämpningsprocessorer som de som baserades på Arm Cortex-A7-kärnan i sin tur dataanalysalgoritmer och körde tillämpningskod på bekanta operativsystem som Linux eller Android.

Framväxten av edge computing-system har tagit tillämpningskodkörningen närmare datakällan. I själva verket har efterfrågan på snabbare respons från mer komplexa analysalgoritmer nu tagit tillämpningsbehandlingskraven till själva slutenheterna. Konsumenterna förväntar sig i allt högre grad att sofistikerade analysfunktioner inklusive artificiell intelligens-metoder är inbyggt i enheter som sakernas internet (IoT) sensorer, bärbara enheter och andra lågeffektprodukter.

Den heterogena flerkärnsbearbetningens roll

Framväxten av HMP-enheter som kombinerar inbäddade och tillämpningsprocessorkärnor har hjälpt utvecklarna att hantera blandade arbetsbelastningar effektivare i många tillämpningar. HMP-processorer integrerar olika kärnor som var och en optimerats för att uppfylla olika krav som är förknippade med målproduktens arbetsbelastning. Med NXP i.MX 7ULP (ultralåg effekt) processorfamiljen kan utvecklarna utnyttja prestandamöjligheterna hos en HMP-arkitektur för att möta konsumenternas krav på höga prestanda och lång batterilivslängd i nästa generations ULP-produkter.

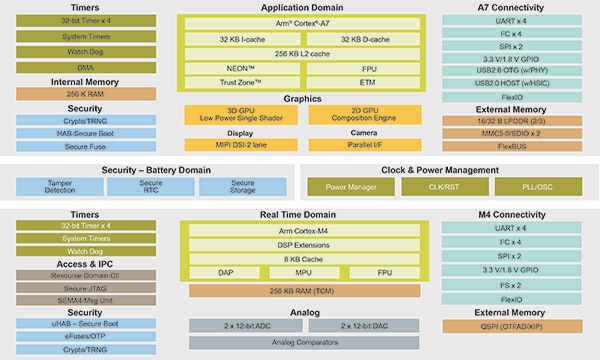

i.MX 7ULP-processorrns finns i version för både konsumenter (MCIMX7U5DVP07SC) och industri (MCIMX7U5CVP06SC) och integrerar sina heterogena kärnor med grafikbehandlingsenheter, säkerhetsacceleratorer, minnesstyrenheter samt en full uppsättning av perifera gränssnitt (figur 1).

Figur 1: Tillsammans med ett omfattande utbud av moduler och kringutrustning kombinerar tillämpningsprocessorfamiljen NXP i.MX 7ULP en Arm Cortex-M4-kärna för realtidsbehandling med en Arm Cortex-A7-kärna för tillämpningsbehandling. Den använder separata effektdomäner för att optimera effekt och prestanda. (Bildkälla: NXP)

Figur 1: Tillsammans med ett omfattande utbud av moduler och kringutrustning kombinerar tillämpningsprocessorfamiljen NXP i.MX 7ULP en Arm Cortex-M4-kärna för realtidsbehandling med en Arm Cortex-A7-kärna för tillämpningsbehandling. Den använder separata effektdomäner för att optimera effekt och prestanda. (Bildkälla: NXP)

NXP i.MX 7ULP-familjen är särskilt utformad för effektbegränsade bärbara konstruktioner och hanterar framväxande krav genom att kombinera en Arm Cortex-A7-kärna med en Cortex-M4-kärna som matas av varsin separat effektdomän. Dessutom innebär användningen av olika effektöar att olika moduler kan drivas selektivt när de inte behövs. Som beskrivs nedan låter sofistikerade strömhanteringsfunktioner som integreras i i.MX 7ULP-enheter användarna använd dessa effektdomäner och effektöar för att ställa in prestanda och effektförbrukning efter sina tillämpningar.

Effektoptimering

När NXP utformade i.MX 7ULP-familjen byggde de in effekt- och prestandaoptimeringsfunktioner i enheter med början på chipnivån och genom hela arkitekturen.

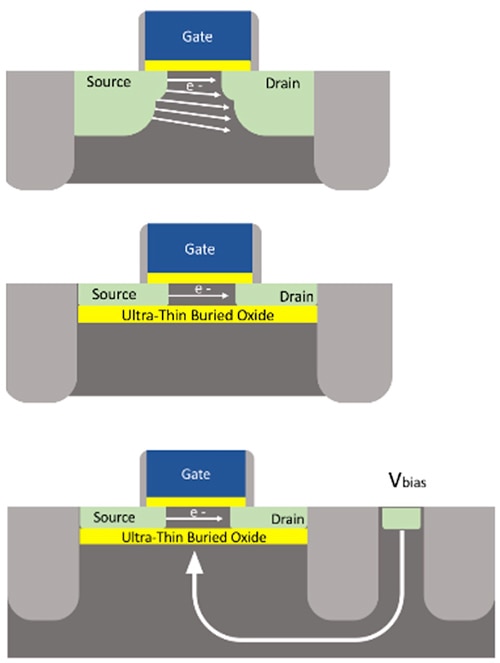

På den mest grundläggande nivån kombinerar i.MX 7ULP-familjen tillverkningsmetoder som minskar läckströmmen med transistorkonstruktioner som sänker parasitströmmar och därigenom minskas den dynamiska effektförbrukningen. Till skillnad från konventionella transistorstrukturer (figur 2, ovan) tillverkas i.MX 7ULP-enheter med en ultratunn infälld oxid (figur 2, mitten) som minskar elektronflödet från källa till förbrukare och därigenom minskar läckströmmen. En ytterligare förbättring tillåter konstruktörerna att lägga till framåtstommebias (FBB) eller bakåtstommebias (RBB) (figur 2, nedan).

Figur 2: En konventionell transistor kan uppvisa betydande läckage vid elektronflöde från källa till förbrukare (ovan), men NXP i.MX 7ULP-familjen tillverkas med ultratunn infälld oxid som minskar elektronflödet (mitten) och en struktur som ytterligare påskyndar eller saktar in elektronflödet med framåtstommebias (FBB) eller bakåtstommebias (RBB) (nedan). (Bildkälla: NXP)

Figur 2: En konventionell transistor kan uppvisa betydande läckage vid elektronflöde från källa till förbrukare (ovan), men NXP i.MX 7ULP-familjen tillverkas med ultratunn infälld oxid som minskar elektronflödet (mitten) och en struktur som ytterligare påskyndar eller saktar in elektronflödet med framåtstommebias (FBB) eller bakåtstommebias (RBB) (nedan). (Bildkälla: NXP)

När energieffektivitet är en topprioritet kan utvecklarna använda RBB för att minska elektronflödet och ytterligare minska läckströmmen och den övergripande enhetseffektförbrukningen till kostnad av lägre prestanda. Omvänt kan utvecklarna använda FBB, som förbättrar elektronflödet, för att förstärka prestandan till kostnad av ökad strömförbrukning på grund av högre läckström.

På chipnivån innefattar i.MX 7ULP-familjen flera tekniker, inklusive dynamisk frekvensskalning (DFS) och dynamisk spänningsskalning (DVS), programvarubaserad klockgrindning samt programvarubaserad effektgrindning. Förutom att minska effektförbrukningen hos olika kringenheter kan utvecklarna använda dessa funktioner för att selektivt stänga av block av internminne eller försätta minnet i olika strömsparlägen.

På arkitekturnivån utökas möjligheten att ställa in effekt och prestanda ytterligare genom användningen av flera effektdomäner inklusive de separata effektdomänerna som nämndes tidigare för Cortex-A7- och Cortex-M4-delsystemen.

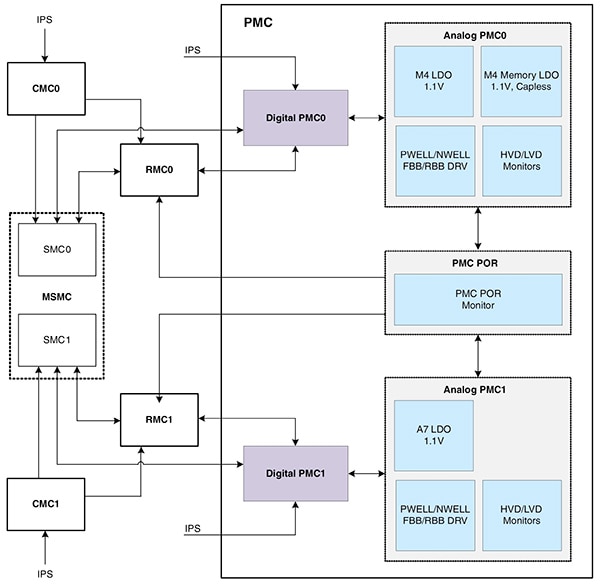

Var och en av processorkärnans strömdomäner inkluderar FBB- och RBB-drivkretsar, dedikerade regulatorer med lågt bortfall (LDO) samt högnivå- (HVD) och lågnivådetektorer (LVD) som är utformade för att signalera tillförselavvikelser över eller under angivna trösklar. En separat power-on-reset-övervakare (PoR) följer spänningsnivån i alltid på-effektdomänen.

Tillsammans med de separata the kärneffektdomänerna styr enskilda effektdomäner även systemfunktioner som alltid på-maskinvara, medan en batteristödd domän hanterar ström till kritiska funktioner inklusive realtidsklockan och en säker icke-flyktig lagringsmodul, bland annat. Precis som för kärneffektdomänerna stödjer var och en av dessa specialiserade effektdomäner en omfattande uppsättning av specialiserade strömbesparande funktioner (som är för många för att tas upp enskilt i en enda artikel).

För att ta ett exempel inkluderar domänen för alltid på-funktion en LLWU-modul (Low-Leakage Wake-Up Unit) som låter utvecklarna använda flera externa stift eller interna moduler som aktiveringskälla för de särskilda lågeffektlägen som beskrivs nedan.

Dessa arkitekturfunktioner kopplas samman i enhetens integrerade effekthanteringsenhet (PMC), som hanterar dessa separata effektdomäner och enhetens effektöar (figur 3).

Figur 3: NXP i.MX 7ULP-familjen innehåller en sofistikerad styrkapacitet som gör att utvecklarna programmatiskt kan konfigurera effektdomäner och effektöar för att ställa in effekt och prestanda för att uppfylla ändrade tillämpningskrav. (Bildkälla: NXP)

Figur 3: NXP i.MX 7ULP-familjen innehåller en sofistikerad styrkapacitet som gör att utvecklarna programmatiskt kan konfigurera effektdomäner och effektöar för att ställa in effekt och prestanda för att uppfylla ändrade tillämpningskrav. (Bildkälla: NXP)

I den här metoden initierar utvecklarna effektlägesövergångar genom att skicka kommandon genom den normala bussen för det smarta delsystemet för kringutrustning (IPS) till ett styrkomplex som består av tre tätkopplade moduler:

- Core Mode Controller (CMC), med stöd för flera kärnfunktioner

- Multicore System Mode Controller (MSMC), som består av System Mode Controller 0 (SMC0) för Cortex-M4-effektdomänen och SMC1 för Cortex-A7-effektdomänen, som hanterar sekvensering mellan olika effektlägen, övervakar händelser som används för att initiera effektlägesövergångar och i allmänhet styr effekt, klocka och minnesfunktioner som är kopplade till effektoptimering

- Reset Mode Controller (RMC), som hanterar chipåterställningsfunktioner

Ställa in effekt och prestanda

Med alla sina effekthanteringsfunktioner tillhandahåller i.MX 7ULP-familjen utvecklarna med en bekant programmeringsmodell. Som andra avancerade processorer uppnår i.MX 7ULP-enheter annorlunda lågeffektdriftlägen genom en serie av programmerbara lågeffektslägen. I själva verket har .MX 7ULP-processorkärnorna stöd för flera programvarustyrda lågeffektslägen som gör det möjligt för utvecklarna att sänka effektförbrukningen till lägsta möjliga nivå i enlighet med önskad funktion.

Med hjälp av dessa olika lågeffektslägen kan utvecklarna ställa in en eller båda kärnorna och deras delsystem i olika variationer av ett normalt RUN-, WAIT- eller STOP-läge.

Normalt RUN-läge och höghastighets-HSRUN-läge ger högpresterande drift för att stödja beräkningsintensiva delar av en tillämpning. I HSRUN-läge arbetar kärndelsystemet på sin högsta frekvens. Om tillämpningen kan klara lägre prestanda kan utvecklarna ställa in kärnan i VLPR-läge (Very Low Power Run) för användning med en maximal frekvens på 48 megahertz (MHz) med motsvarande lägre effektförbrukning.

I normalt WAIT-läge arbetar kringutrustningen fullt, men kärnan är klockgrindad och väntar i statiskt läge, men är klar att aktiveras när en WFI-signal (Wait-For-Interrupt) tas emot. I det här läget kan utvecklarna låta autonoma perifera funktioner fylla buffertar eller använda DMA-transaktioner (direct-memory access) för att fylla systemminnet innan de utfärdar ett avbrott som avbryter kärnans WAIT-status. I VLPW-läge (Very Low Power Wait) kan kringutrustningen fortsätta användas med minskad frekvens, men kärnklockorna grindas.

I tillämpningar som bärbar utrustning kan systemet uppleva längre perioder av inaktivitet som kan brytas av periodiska aktivitetsökningar. I dessa fall är förmågan att spara effekt kritisk för batterilivslängden Om tillämpningen kan tolerera långsammare aktiveringstid för kärnan kan förmågan att försätta enheten i ännu djupare vilolägen än RUN, WAIT eller variationer med mycket låg effekt vara särskilt effektiva alternativ. För att stödja den här metoden kan utvecklarna försätta varje i.MX 7ULP-kärndelsystem i ett djupare viloläge som innebär olika lång aktiveringstid:

- I STOP-status kan vissa kringenheter användas asynkront, men kärnan kvarstår i statisk status med aktiveringstider på 7 mikrosekunder (μs) för Cortex-A7 eller 7 μs för Cortex-M4

- I VLPS-läge (Very Low Power Stop) begränsas perifera funktioner ytterligare, men kärnan kvarstår i statisk status med aktiveringstider på 21,5 μs (Cortex-A7) eller 9 μs (Cortex-M4).

För tillämpningar med ännu striktare effektkrav kan utvecklarna ställa in varje kärna i följande särskilda lågläckagelägen som stänger av fler enhetsdelsystem:

- LLS (Low Leakage Stop), klockgrindar kärnan, bussen och kringutrustningen och lämnar kärnan i WFI-status, vilket ger en aktiveringstid på 40 μs (Cortex-A7) eller 58 μs (Cortex-M4)

- VLLS (Very Low Leakage Stop), klockgrindar kärnans hela effektdomän, vilket ger längre aktiveringstider, inklusive 60 μs för Cortex-A7 eller 375 μs för Cortex-M4

För ännu högre effektbesparingar kan utvecklarna använda RBB i vissa effektlägen inklusive VLPS och LLS med motsvarande minskning i prestanda och en stegvis ökning i aktiveringstid på 2 till 4 μs.

Omvänt gäller att när utvecklarna måste hantera beräkningsintensiva arbetslaster kan de köra kärnorna i ett särskilt HSRUN-läge (high speed run). HSRUN-läget växlar Cortex-A7-kärnan från sin normala 500 MHz-driftfrekvens till ett överklockningsläge på 720 MHz.

Med den här fina kontrollnivån kan utvecklarna konfigurera i.MX 7ULP för att uppfylla även extrema effektkrav utan att offra grundläggande funktion. Till exempel kan en tillämpning behöva lägsta möjliga effektförbrukning, men kräva realtidsfunktionen hos Cortex-M4-kärnan samt användning av specifik kringutrustning eller minne för Cortex-A7-delsystemet. I det här läget kan utvecklaren försätta Cortex-A7-delystemet i STOP- eller VLPS-status och komma åt dess minne eller kringutrustning från Cortex-M4 när den kärnan utför sina realtidsfunktioner. För ytterligare effektbesparingar kan utvecklarna använda Cortex-M4-klockan för att driva Cortex-A7:s kringenheter.

Enkel systemimplementering

För att implementera ett lågeffektsystem med i.MX 7ULP kan utvecklarna välja mellan tillgängliga programvaruprogrammerbara effektlägen och konfigurationer för att matcha kraven på effekt och prestanda. På maskinvarusidan är systemdesignen ännu enklare.

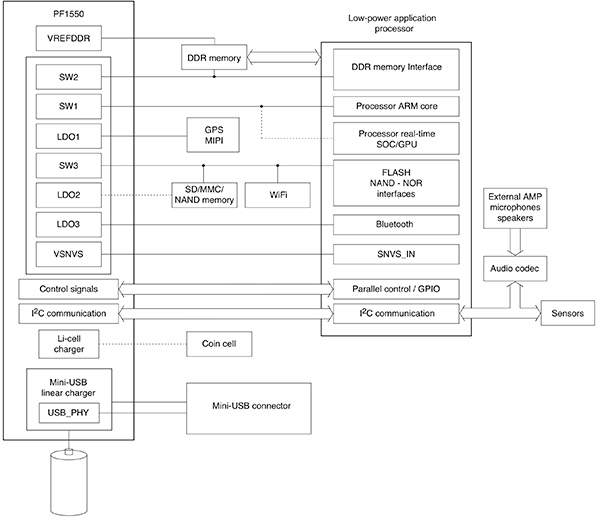

För typiska tillämpningar kan utvecklarna enkelt kombinera en i.MX 7ULP-processor med den medföljande NXP MC32PF1550A3EPR2-effekthanteringskretsen (PMIC) för att slutföra en design som kan hantera blandade arbetslaster utan att kompromissa med begränsade effektbudgetar (figur 4).

Figur 4: Effekthanteringskretsen NXP MC32PF1550A3EPR2 tillhandahåller den kompletta uppsättning av matningskällor som krävs av NXP i.MX 7ULP-processorn och begränsar maskinvarudesignen till en enkel kombination av dessa två enheter och några få passiva komponenter. (Bildkälla: NXP)

Figur 4: Effekthanteringskretsen NXP MC32PF1550A3EPR2 tillhandahåller den kompletta uppsättning av matningskällor som krävs av NXP i.MX 7ULP-processorn och begränsar maskinvarudesignen till en enkel kombination av dessa två enheter och några få passiva komponenter. (Bildkälla: NXP)

MC32PF1550A3EPR2 är särskilt utformad för att stödja kraven hos NXP-processorer som i.MX 7ULP-familjen och integrerar tre omkopplingsspänningsregulatorer (SW1, SW2, SW3), tre LDO-regulatorer (LDO1, LDO2, LDO3), en minnesreferensspänningskälla, en komplett encellig litiumbatteriladdare och engångsprogrammerbart (OTP) minne för enhetskonfiguration.

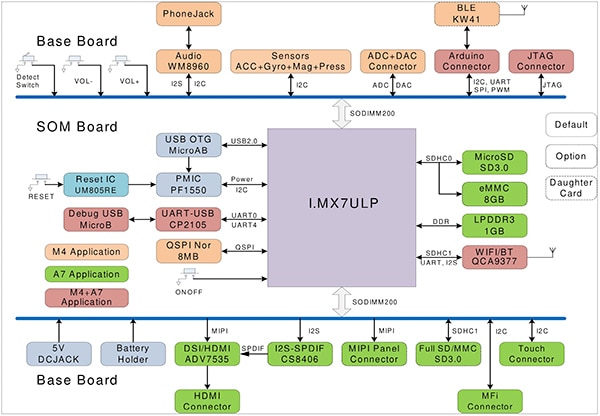

Med sin MCIMX7ULP-EVK-utvärderingssats demonstrerar NXP det enkla maskinvarugränssnitt som behövs för att kombinera MC32PF1550A3EPR2 PMIC och i.MX 7ULP-enheten. Tillsammans med ett SOM-kort (system-on-module) som innehåller i.MX 7ULP-processorn och MC32PF1550A3EPR2 PMIC inkluderar satsen ett baskort med flera sensorer, trådlös kapacitet, en ljudcodec, en SD-kontakt och flera andra kontakter inklusive JTAG och Arduino (figur 5).

Figur 5: Utvärderingssatsen MCIMX7ULP-EVK kombinerar ett SOM-kort som innehåller en i.MX 7ULP-processor och MC32PF1550A3EPR2 PMIC med ett baskort som innehåller sensorer, kontakter och andra komponenter som krävs för att påskynda programvaruutvecklingen med i.MX 7ULP-enheter. (Bildkälla: NXP)

Figur 5: Utvärderingssatsen MCIMX7ULP-EVK kombinerar ett SOM-kort som innehåller en i.MX 7ULP-processor och MC32PF1550A3EPR2 PMIC med ett baskort som innehåller sensorer, kontakter och andra komponenter som krävs för att påskynda programvaruutvecklingen med i.MX 7ULP-enheter. (Bildkälla: NXP)

Medan utvärderingssatsen tillhandahåller direkt funktion tillhandahåller NXP även utvecklarna nedladdningsbara designfiler, verktyg och kortstödpaket för anpassad programvara med FreeRTOS för realtidskod och Linux eller Android för tillämpningskod.

Slutsats

Efterfrågan på både mer sofistikerad funktion och längre batterilivslängd i mobila produkter har traditionellt tvingat utvecklarna till en viss nivå av kompromisser mellan effekt och prestanda. Dessutom har växande förväntan på snabba data från fler sensorer i IoT-enheter, bärbar utrustning och andra bärbara produkter framtvingat ytterligare kompromisser mellan realtidsfunktioner och prestanda på tillämpningsnivå.

Som visas kan dock utvecklarna använda HMP-arkitekturer som de som används i NXP:s i.MX 7ULP-processorfamilj för att uppfylla strikta krav på ultralåg effekt utan att offra funktionen.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.