Co-processorarkitekturen: En inbyggd systemarkitektur för snabb prototypframtagning

2021-07-06

Redaktörens kommentar: Även om co-processorarkitekturen är välkänd för sin digitala processningskapacitet och genomströmning, ger co-processorarkitekturen konstruktörer av inbäddade system möjligheter att leda projekt på sätt som både sänker utvecklingskostnaderna och tidsåtgången för marknadslansering. Denna artikel, som särskilt fokuserar på kombinationen av en diskret microcontroller (MCU) och en diskret fältprogrammerbar grindmatris (FPGA), visar hur denna arkitektur lämpar sig för en effektiv och iterativ konstruktionsprocess. Med hjälp av researchkällor, empiriska resultat och fallstudier utforskas fördelarna med denna arkitektur och exempel på tillämpningar ges. Efter att ha satt sig in i denna artikel, kan konstruktörer av inbyggda system få en bättre förståelse för när och hur denna mångsidiga hårdvaruarkitektur ska implementeras

Inledning

Konstruktörer av inbyggda system befinner sig i en korsning av konstruktionsgränser, prestandaförväntningar samt tids- och budgetbegränsningar. Till och med motsägelserna i de moderna modeorden och fraserna för projektledning understryker ytterligare den ovissa karaktären hos denna roll: "misslyckas snabbt", "var responsiv", "framtidssäkra det" och "var distuptiv!". Den akrobatik som krävs för att ens försöka uppfylla dessa förväntningar kan vara halsbrytande, men ändå florerar uttrycken, och de fortsätter att förstärkas på marknaden. Det som behövs är en konstruktionsmetodik som möjliggör en evolutionär iterativ process, och precis som med de flesta inbyggda system börjar det med hårdvaruarkitekturen.

Co-processorarkitekturen, en hårdvaruarkitektur som är känd för att kombinera styrkorna hos både microcontrollers (MCU) och FPGA:er (Field Programmable Gate Array), kan erbjuda konstruktörer av inbyggda system en process som kan uppfylla även de högsta kraven, men som ändå ger den flexibilitet som krävs för att ta itu med både kända och okända utmaningar. Genom att ta fram hårdvara som kan anpassas iterativt kan konstruktörerna göra framsteg, nå kritiska milstolpar och dra stor nytta av en snabb prototypframtagningsprocess.

Inom denna process finns viktiga projektmilstolpar, var och en med sitt eget unika värde som bidrar till utvecklingsarbetet. I denna artikel benämns dessa med följande begrepp: Milstolpen digital signalbehandling med microcontroller, milstolpen systemförvaltning med microcontroller och milstolpen produktutveckling.

I slutet av denna artikel visas hur en flexibel hårdvaruarkitektur kan vara bättre lämpad för moderna inbäddade system än en mer rigid strategi. Dessutom kan detta tillvägagångssätt leda till både sänkta projektkostnader och kortare tid till marknadslansering. Argument, exempel och fallstudier ges för att försvara denna ståndpunkt. Genom att observera värdet av varje milstolpe inom ramen för den konstruktionsflexibilitet som denna arkitektur ger, blir det tydligt att en adaptiv hårdvaruarkitektur är en kraftfull drivkraft för att driva konstruktionen av inbyggda system framåt.

Upptäck styrkorna hos co-processorarkitekturen: flexibilitet i konstruktion och hög processningsprestanda

En vanlig tillämpning för FPGA-konstruktioner är att vara ett direkt gränssnitt mot en snabb A/D-omvandlare. Signalen digitaliseras, läses in i FPGA:n och sedan appliceras några algoritmer för digital signalprocessning (DSP) av signalen. Slutligen fattar FPGA:n beslut utifrån resultaten.

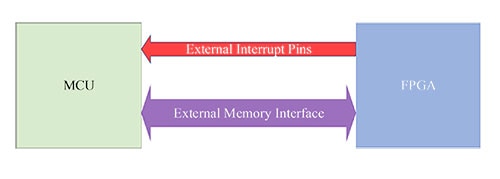

En sådan tillämpning tjänar som exempel i hela denna artikel. Figur 1 illustrerar vidare en generisk co-processorarkitektur där microcontrollern och FPGA:n är anslutna via microcontrollerns externa minnesgränssnitt. FPGA:n behandlas som om den vore ett externt statiskt arbetsminne (SRAM). Signalerna kommer tillbaka till microcontrollern från FPGA:n och fungerar som interruptlinjer och statusindikatorer. Detta gör det möjligt för FPGA:n att indikera kritiska tillstånd till microcontrollern, t.ex. för att meddela att en A/D-omvandling är klar, att ett fel har inträffat eller att en annan speciell händelse har inträffat.

Figur 1: Generiskt schema för en co-processor (microcontroller + FPGA). (Bildkälla: CEPD)

Figur 1: Generiskt schema för en co-processor (microcontroller + FPGA). (Bildkälla: CEPD)

Styrkorna i co-processormetoden framgår förmodligen bäst av resultaten från var och en av de ovan nämnda milstolparna. Värdet avgörs inte bara genom att lista vad en uppgift eller fas har åstadkommit, utan också genom att bedöma den möjlighet som dessa prestationer ger. Svaren på följande frågor hjälper till att bedöma det totala värdet av en delmålsleverans:

- Kan de andra gruppmedlemmarnas framsteg nu fortsätta snabbare, vartefter som beroendekopplingar och flaskhalsar i projektet har eliminerats?

- Hur möjliggör milstolparnas prestationer ytterligare parallella banor till genomförande?

Milstolpen digital signalbehandling med microcontrollern

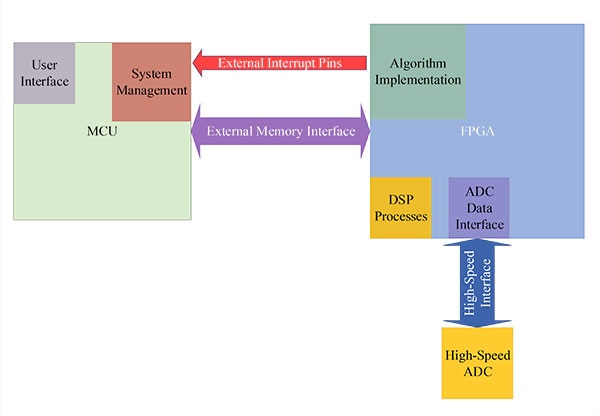

Figur 2: Arkitektur - digital signalbehandling med microcontroller. (Bildkälla: CEPD)

Figur 2: Arkitektur - digital signalbehandling med microcontroller. (Bildkälla: CEPD)

I det första utvecklingsstadiet som denna hårdvaruarkitektur möjliggör finns microcontrollern i centrum. Allt annat lika är utveckling med microcontrollers och körbar programvara mindre resurs- och tidskrävande än utveckling av FPGA:er och HDL (hårdvarudeskriptivt språk). Genom att inleda produktutvecklingen med microcontrollern som primär processor kan algoritmerna implementeras, testas och valideras snabbare. På så sätt kan algoritmiska och logiska fel upptäckas tidigt i konstruktionsprocessen och stora delar av signalkedjan kan testas och valideras.

FPGA:ns roll i denna första milstolpe är att fungera som ett gränssnitt för snabb datainsamling. Dess uppgift är att på ett tillförlitligt sätt leda data från den snabba A/D-omvandlaren, varna microcontrollern om att data är tillgängliga och presentera dessa data på microcontrollerns externa minnesgränssnitt. Även om denna roll inte omfattar implementering av HDL-baserade DSP-processer eller andra algoritmer är den ändå mycket viktig.

FPGA-utvecklingen som utförs i denna fas lägger grunden för produktens slutliga framgång, både inom ramen för utvecklingen av produkten och när den släpps på marknaden. Genom att bara fokusera på lågnivågränssnittet kan tillräckligt med tid avsättas för att testa dessa viktiga funktioner. Det är först när FPGA:n på ett tillförlitligt och säkert sätt utför denna roll, som gränssnitt som denna milstolpe kan slutföras på ett tryggt sätt.

De viktigaste resultaten från denna första milstolpe omfattar följande fördelar:

- Hela signalbanan - alla förstärkningar, dämpningar och omvandlingar - kommer att ha testats och validerats.

- Projektets utvecklingstid och arbete kommer att ha minskat genom att algoritmerna först implementeras i mjukvara (C/C++), vilket är av stort värde för projektledningen och andra intressenter, vilka måste se att projektet är genomförbart innan de godkänner framtida konstruktionsfaser.

- Lärdomarna från implementeringen av algoritmerna i C/C++ kommer att kunna överföras direkt till HDL-implementeringar, med användning av verktyg som omvandlar mjukvara till HDL, t.ex. Xilinx HLS.

Milstolpen systemförvaltning med microcontrollern

Figur 3: Arkitektur - systemförvaltning med microcontroller. (Bildkälla: CEPD)

Figur 3: Arkitektur - systemförvaltning med microcontroller. (Bildkälla: CEPD)

Det andra utvecklingssteget som denna co-processorstrategi erbjuder, definieras genom att DSP-processer och algoritmimplementeringar flyttas från microcontrollern till FPGA:n. FPGA:n är fortfarande ansvarig för det snabba A/D-omvandlargränssnittet, men genom att ta på sig även dessa andra roller utnyttjas FPGA:ns hastighet och parallellitet fullt ut. Till skillnad från microcontrollern, kan dessutom flera instanser av DSP-processer och algoritmkanaler implementeras och köras samtidigt.

Konstruktören kan bygga vidare på de erfarenheter som gjorts från microcontrollerimplementeringen, och ta med sig detta till nästa milstolpe. Verktyg som t.ex. det tidigare nämnda Vivado HLS från Xilinx erbjuder en funktionell översättning från den körbara C/C++-koden till syntetiserbart HDL. Nu måste tidsbegränsningar, processparametrar och andra användarpreferenser fortfarande definieras och implementeras, men kärnfunktionaliteten bevaras och översätts till FPGA-funktionen.

Vid denna milstolpe är microcontrollerns roll att vara en systemförvaltare. Status- och styrregister i FPGA:n övervakas, uppdateras och rapporteras av microcontrollern. Dessutom hanterar microcontrollern användargränssnittet (UI). Användargränssnittet kan utgöras av en webbserver som nås via en Ethernet- eller Wi-Fi-anslutning eller ett industriellt pekskärmsgränssnitt mot användarna. Den viktigaste lärdomen av microcontrollerns nya, mer sofistikerade roll är följande: genom att microcontrollern och FPGA:n har befriats från de beräkningsintensiva processoruppgifterna, utnyttjas nu både microcontrollern och FPGA:n för uppgifter som de är väl lämpade för.

De viktigaste resultaten från denna milstolpe omfattar dessa fördelar:

- Snabb, parallell körning av DSP-processer och algoritmimplementationer sköts av FPGA:n.Microcontrollern ger ett responsivt och smidigt användargränssnitt och hanterar produktens processer.

- Efter att först ha utvecklats och validerats i microcontrollern har de algoritmiska riskerna minskats och dessa minskningar kan i sin tur översättas till syntetiserbart HDL. Verktyg som Vivado HLS gör denna översättning enklare. Dessutom kan FPGA-specifika risker minskas med hjälp av integrerade simuleringsverktyg, t.ex. designmjukvaruserien Vivado.

- Olika projektintressenter tar inte någon större risk genom att flytta över processerna till FPGA. Tvärtom får de uppleva och dra nytta av de fördelar som FPGA:s snabbhet och parallellitet ger. Mätbara prestandaförbättringar observeras och fokus kan nu läggas på att göra konstruktionen redo för tillverkning.

Milstolpen produktlansering

Med den beräkningsintensiva processningen i FPGA:n och med microcontrollern som sköter systemhanteringen och användargränssnittet är produkten redo för användning. I detta dokument förespråkas inte att man ska undvika alfa- och beta-utgåvor, men poängen med denna milstolpe ligger i de möjligheter som co-processorarkitekturen ger för slutproduktframtagning.

Både microcontrollern och FPGA:n är enheter som kan uppdateras i fält. Flera framsteg har gjorts för att göra FPGA-uppdateringar lika tillgängliga som mjukvaruuppdateringar. Eftersom FPGA:n ligger inom microcontrollerns adresserbara minnesutrymme, kan microcontrollern dessutom fungera som åtkomstpunkt för hela systemet: den tar emot uppdateringar både för sig själv och för FPGA:n. Uppdateringar kan schemaläggas, distribueras och anpassas för varje slutanvändare. Slutligen kan loggar över användare och användningsfall underhållas och associeras med specifika implementationer av specifika versioner. Med hjälp av dessa datamängder kan prestandan ytterligare förfinas och förbättras även efter att produkten är ute i fält.

Kanske är det som mest i rymdbaserade tillämpningar som fördelarna i dessa uppdateringsmöjligheter för hela systemet framhävs. När en produkt väl har lanserats måste underhåll och uppdateringar utföras på distans. Detta kan vara så enkelt som att ändra logiska villkor eller så komplicerat som att uppdatera ett schema för kommunikationsmodulering. Den programmerbarhet som erbjuds av FPGA-tekniken och co-processorarkitekturen kan rymma hela detta utbud av funktioner, samtidigt som strålningshärdade komponenter finns att välja bland.

Det slutliga viktiga resultatet från denna milstolpe är en progressiv kostnadsminskning. Kostnadsminskningar, ändringar i komponentlistor och andra optimeringar kan också ske vid denna milstolpe. Vid installation i fält kan det visa sig att produkten fungerar lika bra med en billigare microcontroller eller en FPGA med lägre prestanda. Tack vare co-processorn är arkitekturkonstruktörerna inte låsta till att använda komponenter vars kapacitet överstiger tillämpningsbehoven. Om en komponent skulle bli otillgänglig, gör arkitekturen det dessutom möjligt att integrera nya komponenter i konstruktionen. Detta är inte fallet med en ett-chipsarkitektur, ett System on Chip-arkitektur (SoC), eller med en högpresterande DSP eller microcontroller som försöker hantera hela produktens processning. Co-processorarkitekturen är en bra blandning av kapacitet och flexibilitet som ger konstruktörer fler valmöjligheter och friheter, både under utvecklingsfaserna och när produkten lanseras på marknaden.

Stödjande forskning och relaterade fallstudier

Exempel på satellitkommunikation

Kort sagt är värdet av en co-processor att avlasta den primära processorn, så att uppgifterna utförs på hårdvara, där accelerationer och effektiviseringar kan utnyttjas. Fördelen med ett sådant konstruktionsval är en nettoökning av beräkningshastighet och -kapacitet och, som denna artikel hävdar, reducerade kostnader och tid för utveckling. Ett av de mest övertygande tillämpningarna för dessa fördelar är kanske rymdkommunikationssystem.

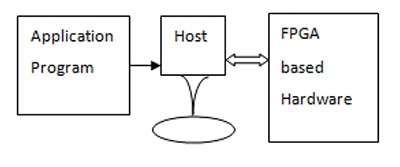

I deras publikation FPGA based hardware as coprocessor, beskriver G. Prasad och N. Vasantha hur databehandling i en FPGA kombinerar satellitkommunikationssystemens beräkningsbehov utan de höga engångskostnaderna för tillämpningsspecifika integrerade kretsar (ASIC) eller de tillämpningsspecifika begränsningarna hos en processor med hård arkitektur. Precis som beskrivits i milstolpen digital signalbehandling med microcontroller börjar deras konstruktion med att applikationsprocessorn utför majoriteten av de beräkningsintensiva algoritmerna. Från denna utgångspunkt identifierar de vilka mjukvarusektioner som förbrukar majoriteten av processorns cykler och flyttar över dessa sektioner till HDL-implementering. Den grafiska framställningen är mycket lik den som hittills har presenterats, men de har valt att representera applikationssprogrammet som ett eget oberoende block, eftersom det antingen kan förverkligas i värddatorn (processorn) eller i den FPGA-baserade maskinvaran.

Figur 4: Applikationsprogram, värdprocessor och FPGA-baserad hårdvara, som används i satellitkommunikationsexemplet.

Figur 4: Applikationsprogram, värdprocessor och FPGA-baserad hårdvara, som används i satellitkommunikationsexemplet.

Genom att använda ett PCI-gränssnitt (Peripheral Component Interconnect) och värdprocessorns direkta minnesåtkomst (DMA) ökar kringkretsarnas prestanda dramatiskt. Detta observeras främst i förbättringarna av avrandomiseringsprocessen. När denna process kördes i värdprocessorns programvara fanns det en tydlig flaskhals i systemets realtidssvar. När den flyttades till FPGA:n kunde följande fördelar iakttas:

- Avrandomiseringsprocessen utförs i realtid utan att orsaka flaskhalsar

- Värdprocessorns beräkningsbörda minskade avsevärt och den kunde nu bättre utföra den önskade loggningsrollen.

- Den totala prestandan för hela systemet systemets förbättrades.

Allt detta uppnåddes utan de kostnader som är förknippade med en ASIC och med den flexibilitet som programmerbar logik ger [5]. Satellitkommunikation innebär stora utmaningar, och denna metodik kan på ett verifierbart sätt uppfylla dessa krav, samtidigt som det ger flexibilitet i konstruktionen.

Exempel på infotainment för bilar

Infotainmentsystem i bilar är viktiga för kräsna konsumenter. Till skillnad från majoriteten av fordonselektronik är dessa enheter mycket synliga och förväntas ge exceptionell responstid och prestanda. Konstruktörerna har dock ofta svårt att hitta en lösning som är anpassad till de aktuella behoven och den flexibilitet som framtida funktioner kommer att kräva. I detta exempel kommer behoven av signalbehandling och trådlös kommunikation att användas för att belysa styrkorna med med hårdvarusidan av co-processor-arkitekturen.

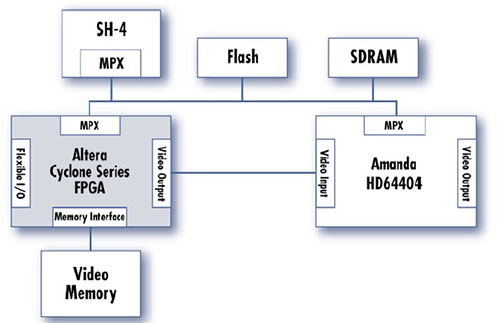

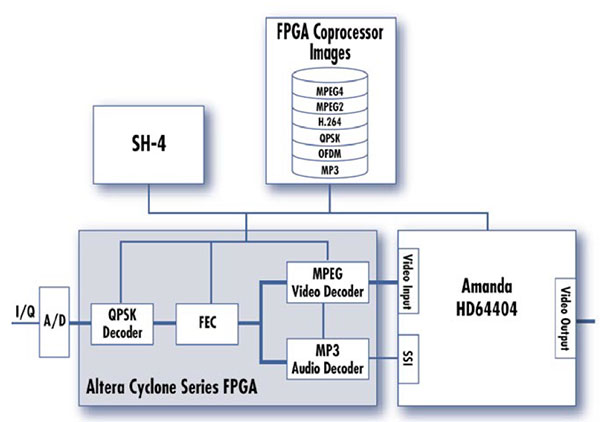

En av de dominerande arkitekturerna för underhållningssystem för bilar publicerades av Delphi Delco Electronics Systems Corporation. Denna arkitektur använde en SH-4-microcontroller med en tillhörande ASIC, Hitachis hjälpkrets HD64404 Amanda. Denna arkitektur uppfyllde mer än 75 % av fordonsmarknadens grundläggande underhållningsfunktionalitet, men den saknade möjlighet att hantera videoprocessningstillämpningar och trådlös kommunikation. Genom att inkludera en FPGA i denna befintliga arkitektur kan mer flexibilitet och kapacitet byggas in i denna befintliga konstruktionsmetodik.

Figur 5: FPGA-baserad co-processor-arkitektur i infotainmentsystem, exempel 5.

Figur 5: FPGA-baserad co-processor-arkitektur i infotainmentsystem, exempel 5.

Arkitekturen i figur 5 lämpar sig för både videoprocessning och hantering av trådlös kommunikation. Genom att flytta DSP-funktionerna till FPGA:n kan Amanda-processorn fungera som systemförvaltare och kan frigöras för att implementera en trådlös kommunikationsstack. Eftersom både Amanda och FPGA har tillgång till det externa minnet kan data snabbt utbytas mellan systemets processorer och komponenter.

Figur 6: FPGA-baserad co-processor-arkitektur i infotainmentsystem, exempel 2.

Figur 6: FPGA-baserad co-processor-arkitektur i infotainmentsystem, exempel 2.

Den andra infotainmentfilmen i figur 6 visar FPGA:ns förmåga att sköta både snabbt inkommande analog data och att hantera den komprimering och kodning som krävs för videotillämpningar. Faktum är att all denna funktionalitet kan placeras i FPGA:n och med hjälp av parallell processning kan alla dessa funktioner skötas i realtid.

Genom att inkludera en FPGA i en befintlig hårdvaruarkitektur kan den befintliga hårdvarans beprövade prestanda kombineras med flexibilitet och framtidssäkring. Även inom befintliga system ger co-processorarkitekturen konstruktörer alternativ som annars inte skulle vara tillgängliga [6].

Fördelar med snabba prototypframtagning

I grund och botten eftersträvar processen för snabb prototypframtagning att täcka in en stor del av produktutvecklingsområdet, genom att utföra uppgifter parallellt, identifiera "buggar" och konstruktionsproblem snabbt och validera data- och signalvägar, särskilt de som ingår i projektets kritiska utvecklingsbana. Men för att denna process verkligen ska ge strömlinjeformade och effektiva resultat måste det finnas tillräcklig expertis inom respektive projektområden.

Traditionellt sett innebär detta att det måste finnas en maskinvaruingenjör, en ingenjör för inbyggd programvara eller DSP-teknik och en HDL-ingenjör. Nu finns det gott om tvärvetenskapliga yrkesverksamma som kan fylla flera olika roller, men det finns fortfarande en betydande projektkostnad för att samordna dessa insatser.

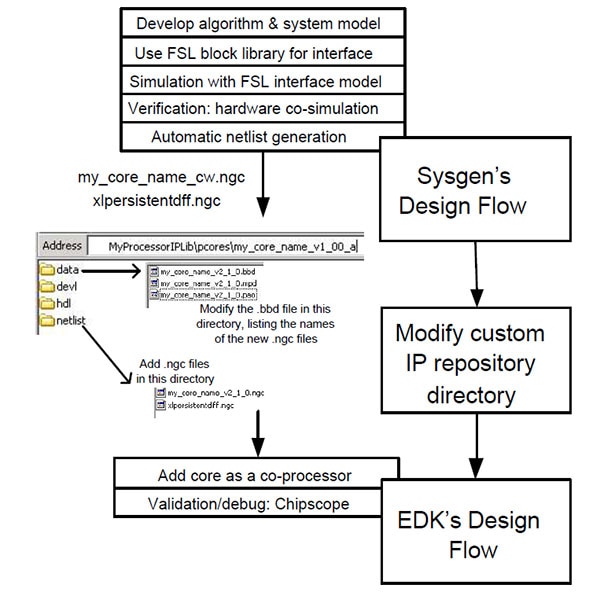

I sin artikel An FPGA based rapid prototyping platform for wavelet coprocessors (En FPGA-baserad plattform för snabba prototyper för co-processorer för wavelet) framhåller författarna idén att en co-processorarkitektur gör det möjligt för en enda DSP-ingenjör att fylla alla dessa roller på ett effektivt sätt. För denna studie började teamet att utforma och simulera den önskade DSP-funktionen i MATLAB:s Simulink-verktyg. Detta hade två primära funktioner, eftersom det 1) verifierade den önskade prestandan genom simulering och 2) fungerade som en grundnivå som framtida konstruktionsval kunde jämföras med och referera till.

Efter simuleringen identifierades kritiska funktioner och delades upp i olika kärnor - dessa är mjukvarukärniga komponenter och processorer som kan syntetiseras i en FPGA. Det viktigaste steget i detta arbete var att definiera gränssnittet mellan dessa kärnor och komponenter och att jämföra datautbytesprestandan med den önskade, simulerade prestandan. Denna konstruktionsprocess stämde väl överens med Xilinx-konstruktionsflödet för inbäddade system och sammanfattas i figur 7 nedan.

Figur 7: Flöde för utformning av implementationen.

Figur 7: Flöde för utformning av implementationen.

Genom att dela upp systemet i syntetiserbara kärnor kan DSP-ingenjören fokusera på de mest kritiska aspekterna av signalbehandlingskedjan. Hen behöver inte vara expert på hårdvara eller HDL för att modifiera, dirigera eller implementera olika mjukkärneprocessorer eller komponenter i FPGA:n. Så länge konstruktören är medveten om gränssnittet och dataformaten har hen full kontroll över signalvägarna och kan förbättra systemets prestanda.

Empiriska resultat - en fallstudie av den diskreta cosinustransformen

De empiriska resultaten bekräftade inte bara den flexibilitet som co-processorarkitekturen ger konstruktören av inbyggda system, utan visade också på de prestandaförbättrande alternativ som finns tillgängliga med moderna FPGA-verktyg. Förbättringar, som de som nämns nedan, kanske inte är tillgängliga eller har mindre effekt för andra maskinvaruarkitekturer. Den diskreta cosintransformen (DCT) valdes ut som en beräkningsintensiv algoritm, och dess utveckling från en C-baserad implementering till en HDL-baserad implementering har stått i centrum för dessa resultat. DCT valdes eftersom denna algoritm används inom digital signalbehandling för mönsterigenkänning och -filtrering [8]. De empiriska resultaten baserades på en laboratorieövning som utfördes av författaren och hans medarbetare för att erhålla Xilinx Alliance Partner-certifiering för 2020-2021.

Följande verktyg och komponenter användes i detta arbete:

- Vivado HLS v2019

- Bedömnings- och simuleringsenheten var xczu7ev-ffvc1156-2-e

DCT-algoritmen, som börjar med en C-baserad implementering, tar emot två arrayer med 16-bitarstal; array "a" är utgångsarrayen till DCT och array "b" är utgångsarrayen från DCT. Databredden (DW) definieras därför som 16, och antalet element i arrayerna (N) är 1024/DW, dvs. 64. Slutligen är storleken på DCT-arrayen (DCT_SIZE) satt till 8, vilket betyder att en 8x8-array används.

Enligt antagandet i denna artikel gör den C-baserade algoritmimplementationen det möjligt för konstruktören att snabbt utveckla och validera algoritmens funktionalitet. Även om det är en viktig aspekt, är funktionaliteten i denna validering viktigare än exekveringstiden. Denna viktning tillåts eftersom den slutliga implementeringen av denna algoritm kommer att ske i en FPGA, där hårdvaruacceleration, loop unrolling och andra tekniker är lätt tillgängliga.

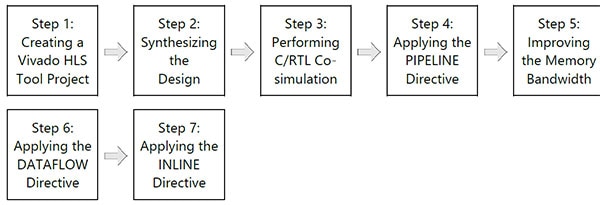

Figur 8: Xilinx Vivado HLS-konstruktionsflödet.

Figur 8: Xilinx Vivado HLS-konstruktionsflödet.

När DCT-koden har skapats som ett projekt i Vivado HLS-verktyget, är nästa steg att börja syntetisera konstruktionen för FPGA-implementering. I detta nästa steg blir några av de mest påtagliga fördelarna med att flytta algoritmens exekvering från en microcontroller till en FPGA tydligare - som referens motsvarar detta steg milstolpen systemhantering med microcontroller som togs upp ovan.

Moderna FPGA-verktyg möjliggör en rad optimeringar och förbättringar som avsevärt förbättrar prestandan hos komplexa algoritmer. Innan du analyserar resultaten finns det några viktiga termer att tänka på:

- Latency - Antalet klockcykler som krävs för att utföra alla iterationer av slingan [10]

- Intervall - Antalet klockcykler innan nästa iteration av en slinga börjar bearbeta data [11]

- BRAM - Block Random Access Memory (blockarbetsminne)

- DSP48E - DSP-slice för UltraScale-arkitekturen

- FF - Flipflop

- LUT - Uppslagstabell

- URAM - Unified Random Access Memory (kan bestå av en enda transistor)

|

||||||||||||||||||||||||||||||||||||||||

Tabell 1: Resultat av optimeringen av FPGA-algoritmens exekvering (latenstid och intervall).

|

Tabell 2: Resultat av optimeringen av FPGA-algoritmens utförande (resursutnyttjande).

Standard

Den vanliga optimeringsinställningen kommer från det oförändrade resultatet av översättningen av den C-baserade algoritmen till syntetiserbart HDL. Inga optimeringar är aktiverade, och detta kan användas som en prestandareferens för att bättre förstå de andra optimeringarna.

Pipeline-innerslinga

PIPELINE-direktivet instruerar Vivado HLS att "unrolla" de inre slingorna så att ny data kan börja processas medan befintlig data fortfarande befinner sig i pipelinen. Nya uppgifter behöver alltså inte vänta på att de befintliga uppgifterna ska vara färdiga innan processningen kan börja.

Pipeline-ytterslinga

Genom att använda PIPELINE-direktivet på ytterslingan, är dennas operationer nu pipelinade. Dock sker nu innerslingornas operationer samtidigt. Både latenstiden och intervalltiden halveras genom att tillämpa detta direkt på ytterslingan.

Arraypartitionering

Detta direktiv mappar innehållet i slingorna till arrayer och plattar därmed till all minnesåtkomst till enskilda element i dessa arrayer. Detta innebär att mer RAM-minne används, men algoritmens körtid halveras.

Dataflöde

Detta direktiv gör det möjligt för konstruktören att specificera önskat antal klockcykler mellan varje inläsning. Detta direktiv stöds endast för toppnivåfunktioner. Endast slingor och funktioner som processas på denna nivå omfattas av detta direktiv.

Inline

INLINE-direktivet plattar ut alla slingor, både inre och yttre. Både rad- och kolumnprocesser kan nu köras samtidigt. Antalet nödvändiga klockcykler hålls till ett minimum, även om detta förbrukar mer FPGA-resurser.

Slutsats

Hårdvaruarkitekturen för co-processorer ger konstruktörer av inbyggda system en plattform med hög prestanda som behåller sin konstruktionsflexibilitet under hela utvecklingen och efter produktlanseringen. Genom att först validera algoritmer i C eller C++ kan processer, data- och signalvägar och kritisk funktionalitet verifieras på relativt kort tid. Genom att översätta processorkrävande algoritmer till co-processor-FPGA:n, kan konstruktören dra nytta av hårdvaruacceleration och en mer modulär konstruktion.

Om vissa delar skulle bli föråldrade eller om optimeringar skulle krävas, kan samma arkitektur möjliggöra dessa ändringar. Nya microcontrollers och nya FPGA:er kan integreras i konstruktionen, samtidigt som gränssnitten kan förbli relativt oförändrade. Eftersom både microcontrollern och FPGA:n kan uppdateras i fält kan dessutom användarspecifika ändringar och optimeringar göras i fält och på distans.

Avslutningsvis kan man säga att denna arkitektur kombinerar utvecklingshastigheten och tillgängligheten hos en microcontroller med prestandan och utbyggbarheten hos en FPGA. Med optimeringar och prestandaförbättringar tillgängliga i varje utvecklingssteg klarar co-processorarkitekturen av att uppfylla även de mest utmanande kraven - både i dagens konstruktioner och i framtiden.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.