Uppfyll olika funktions- och säkerhetskrav med processorer med flera kärnor

Bidraget med av DigiKeys nordamerikanska redaktörer

2020-10-01

Fordon, industri, robotik, byggnadsstyrning och -övervakning och -övervakning och andra kritiska inbäddade systemapplikationer förväntas få bära mer varierande arbetsbelastningar, från strömsnål övervakning i realtid till multimediaapplikationer på hög nivå med grafiska multi-skärmar för människa-maskin-gränssnitt (HMI). Samtidigt som de uppfyller dessa breda funktionella krav måste de också kunna stödja stränga säkerhetsstandarder, lägre kostnad och fotavtryck och optimera effekt / prestanda-balansen.

För att möta dessa ofta ibland motstridiga krav har utvecklare hittills tvingats antingen offra funktionell förmåga eller komplicera design och tillverkning med tillagda enheter som behövs för att stödja specifika krav för grafik, säkerhet och säkerhet, bland andra. Vad utvecklare verkligen behöver är en enda lösning som kan stödja ett brett utbud av produkter som uppfyller dessa krav inom ett brett spektrum av kritiska, inbäddade systemapplikationer.

Den här artikeln beskriver snabbt utvecklingen av kritisk inbäddad systemdesign. Det kommer sedan att visa hur flerkärniga applikationsprocessorer - designade specifikt avNXP Semiconductors för att stödja en snabbt växande lista över krav på både bred funktionalitet och säkerhetscertifierbara funktioner - kan användas för att hantera utvecklarnas utmaningar.

Utvecklingen av inbäddade systemdesignhänsyn

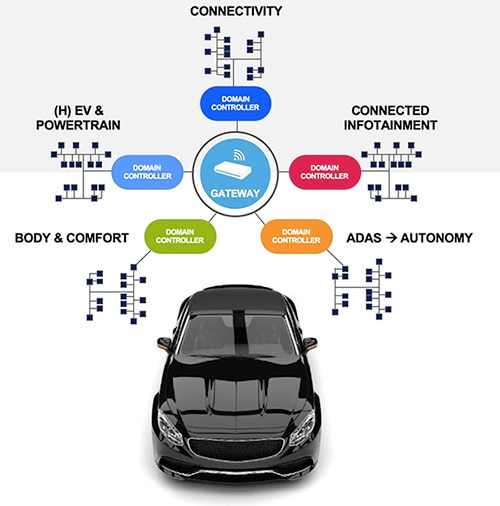

Den traditionella rollen för inbäddade enheter för att stödja en begränsad uppsättning systemfunktioner har till stor del ersatts av efterfrågan på enheter med bred kapacitet. I industriella applikationer kräver till exempel behovet av förbättrade HMI-funktioner i smarta verktyg och utrustning processorer som kan leverera optimerad grafik samtidigt som de uppfyller mer traditionella industriella realtidsbehov. På samma sätt driver trenden i fordonsapplikationer mot hierarkiska arkitekturer som innefattar funktionella domänkluster och gateways ett behov av processorer som fullt ut kan uppfylla dessa krav (Figur 1).

Figur 1: Trenden mot mer hierarkiska bilsystemsarkitekturer har skapat ett behov av mer integrerade, skalbara processorlösningar. (Bildkälla: NXP Semiconductors)

Figur 1: Trenden mot mer hierarkiska bilsystemsarkitekturer har skapat ett behov av mer integrerade, skalbara processorlösningar. (Bildkälla: NXP Semiconductors)

Inom varje funktionell domän fortsätter efterfrågan på mer sofistikerade funktioner att höja tröskeln för prestanda och integrerade funktioner. Till exempel kräver framväxten av heads-up-skärmar lösningar som kan säkerställa fortsatt leverans av viktig grafisk information till förare. Tillsammans med dessa nästa generations skärmar lägger det växande behovet av ökad förarkännedom till ytterligare krav för kameragränssnitt och högpresterande exekvering av avancerad igenkänningsprogramvara som kan ge dåsighet.

I takt med att applikationerna fortsätter att utvecklas blir behovet av mycket integrerade, skalbara lösningar mer angeläget för att möta alltmer olika krav samtidigt som designfotavtryck, kostnad och komplexitet minimeras. Använda NXPi.MX 8 familj av applikationsprocessorer, kan utvecklare utnyttja en kompatibel plattform av processorer med de funktioner och prestanda som behövs för att stödja ett brett spektrum av applikationskrav. Inom i.MX 8-familjen, NXPi.MX 8X serien tillgodoser framväxande behov av säkerhetscertifierbara processorer som krävs för mellan- och industriapplikationer.

Multicore-arkitektur hanterar olika arbetsbelastningar

En av svårigheterna som utvecklare står inför med att implementera enheter för fordons- och industriapplikationer är den stora bredden av kraven. Där utvecklare kunde förvänta sig att hantera antingen realtids- eller högnivåbearbetning av applikationsbearbetningar har efterfrågan på intelligenta delsystem sammanfört dessa väsentligt olika typer av datorer. I allt högre grad behöver utvecklare lösningar som kan leverera både tillförlitlig realtidsrespons och högpresterande applikationskörning samtidigt som de stöder funktionella säkerhetskrav.

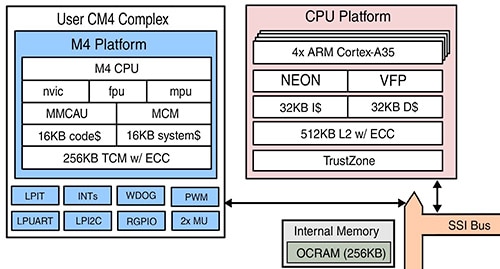

Designade för att leverera realtidsfunktioner, högpresterande bearbetning och låg energiförbrukning, NXP i.MX 8X-serieprocessorer drar full nytta av en sofistikerad flerkärnig processor (CPU) för att hantera olika beräkningsarbetsbelastningar (Figur 2).

Figur 2: NXP i.MX 8X-serien använder en flerkärnig arkitektur som innehåller enÄrm Inbyggd Cortex-M4 (CM4) processor och flera Arm Cortex-A35 applikationsprocessorer för att stödja arbetsbelastningar för blandad programvara. (Bildkälla: NXP Semiconductors)

Figur 2: NXP i.MX 8X-serien använder en flerkärnig arkitektur som innehåller enÄrm Inbyggd Cortex-M4 (CM4) processor och flera Arm Cortex-A35 applikationsprocessorer för att stödja arbetsbelastningar för blandad programvara. (Bildkälla: NXP Semiconductors)

För allmänna ändamål i realtidsbearbetningsuppgifter inkluderar i.MX 8X-enheter en Arm Cortex-M4 (CM4) -processor med flytande punktenhet (FPU), minneskyddsenhet (MPU), minneskartad kryptografisk accelerationsenhet (MMCAU) och diverse styrmodul (MCM). För att stödja extern kringutrustning som sensorer och ställdon, kombinerar detta CM4-användarkomplex en kapslad vektorinterruptcontroller (NVIC) med en omfattande uppsättning gränssnitt och moduler, inklusive strömsnål periodisk avbrottstimer (LPIT), pulsbreddsmodulering (PWM) och andra funktioner som vanligtvis behövs i fordons- och industritillämpningar. Ett par cacheminnen och tätt kopplat minne (TCM) med ECC-felkorrigeringskod bidrar till att minimera åtkomsten till externt minne, snabba upp körningen och hantera minnesfelen.

För snabb körning av applikationsarbetslaster innehåller CPU-plattformen flera energisnåla Arm Cortex-A35-applikationsprocessorer (AP) - två AP i 8DualXPlus-processorer somMIMX8UX6AVLFZAC och fyra AP i 8QuadXPlus-processorer somMIMX8QX6AVLFZAC. Tillsammans med dedikerad instruktionscache (I$) och data (D$) innehåller CPU-plattformen en delad 512 Kbyte stor nivå 2-cache (L2) med ECC.

Arkitekturens Arm Cortex-A35-kärnor ger både mjukvarukompatibilitet och prestandaskalbarhet, vilket stödjer både 32-bitars bakåtkompatibilitet och 64-bitars prestanda. För att påskynda exekveringen av beräkningsintensiva algoritmer som signalbehandling och maskininlärning, erbjuder Arm Cortex-A35-processorerna expansioner för vektorflyttalsprocessning (VFP) och Arms Neon Single Instruction Multiple Data-arkitektur (SIMD). För att snabba upp körning av programvara för bildbehandling, datorsyn och maskininlärning, erbjuder ArmCompute Library funktioner som är optimerade för Arm-processor- och grafikprocessorer (GPU) och Ne10 C-biblioteket med öppen källkod erbjuder Arm-optimerade funktioner för beräkningsintensiva operationer.

Specialprocessorer avlastar primärprocessorerna

Utöver användar-CM4-komplexet och den flerkärniga processorplattformen Arm Cortex-A35, erbjuder arkitekturen ytterligare specialprocessorer för multimediaapplikationer. Tillsammans med en digital signalprocessor (DSP) för ljud- och röst-codec-processning, integrerar arkitekturen både en grafikprocessor och en videoprocessor (VPU). Enhetens grafikprocessor stöder standardgrafikbibliotek, accelererar operationer med fyra separata 4-komponents flyttalsvektorer (vec4) med 16 exekveringsenheter och en 2-dimensionell bitblit-motor med hög prestanda. VPU:n hanterar populära videoformat, accelererar avkodning med upp till 4Kp30 (progressiv, 30 Hz) och kodning med upp till 1080p30. Kretsens dedikerade displaystyrblock kan i sin tur driva grafikutdata till så många som tre oberoende skärmar.

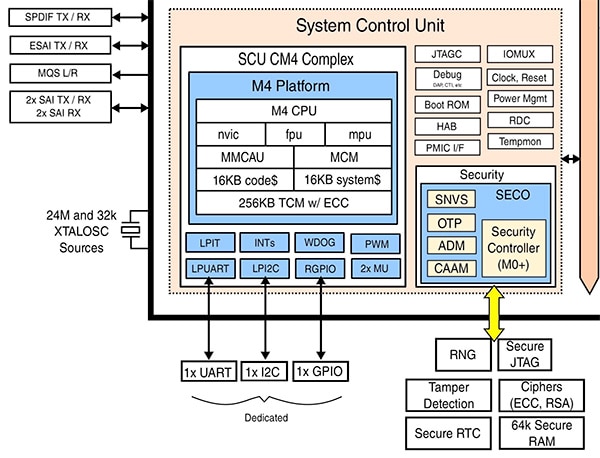

För att ytterligare maximera prestandan integrerar i.MX 8X-arkitekturen också ytterligare processorkärnor som är utformade för att befria de primära CPU-plattformarna från den extra processbelastningen som vanligtvis uppstår vid utförande av systemhanterings- och säkerhetstjänster. För systemhantering inbegriper arkitekturens systemstyrenhet (SCU) ett CM4-komplex som matchar användarens CM4-komplex, samtidigt som den förblir helt dedikerad till SCU-operationer och inte tillgänglig att använda för utvecklare (Figur 3).

Figur 3: Systemstyrenheten, som är integrerad djupt i NXP i.MX 8X-processorerna och inte är tillgänglig för utvecklarna, använder ett dedikerat subsystem, Arm Cortex-M4 (CM4), för att avlasta enhetens huvudprocessorer från systemhanteringsuppgifter. (Bildkälla: NXP Semiconductors)

Figur 3: Systemstyrenheten, som är integrerad djupt i NXP i.MX 8X-processorerna och inte är tillgänglig för utvecklarna, använder ett dedikerat subsystem, Arm Cortex-M4 (CM4), för att avlasta enhetens huvudprocessorer från systemhanteringsuppgifter. (Bildkälla: NXP Semiconductors)

Tillsammans med hantering av strömförsörjning, klockning och andra interna funktioner kontrollerar SCU:n pinnmultiplexering och I/O-kanaldrivstyrka i normal drift. Faktum är att användarens CM4-komplex och Arm Cortex-A35 AP inte kan komma åt dessa olika hårdvarufunktioner på låg nivå. Istället tjänar SCU:n till att abstrahera dessa funktioner, så programvaran som körs på användarens CM4 eller AP behöver bara anropa SCU:ns firmware-API för att utföra funktioner som att stänga av onödiga strömdomäner. Om denna strömdomän exempelvis delas med en annan processor, mottar SCU:n avstängningsbegäran men håller domänen strömsatt tills den andra processorn också lämnar en avstängningsbegäran.

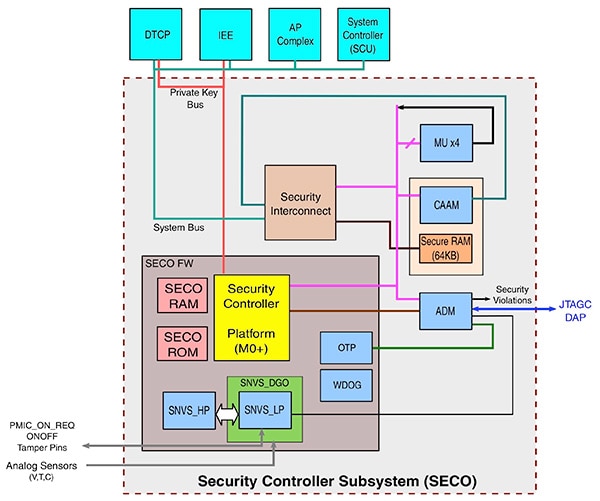

För att hantera i.MX 8X-enhetens omfattande säkerhetsstöd finns också en annan dedikerad processor i enhetens säkerhetsstyrningssystem (SECO). Inom SECO-delsystemet kör en integrerad strömsnål Arm Cortex-M0+-processor med firmware som stöder maskinvarubaserade säkerhetsfunktioner, inklusive en privat bussåtkomst för säkra nycklar, ett engångsprogrammerbart (OTP) minne för säker nyckellagring och säker icke-flyktig lagring (SNVS) för tillkommande privat data eller kortvariga nycklar (Figur 4).

Figur 4: Inom subsystemet NXP i.MX 8X security controller (SECO) hanterar en dedikerad Arm Cortex-M0+-processor säkerhetsoperationer, som bygger på en privat nyckelbuss och flera hårdvarumoduler för säker lagring, kryptografiacceleration och autentiserad åtkomst till debugging. (Bildkälla: NXP Semiconductors)

Figur 4: Inom subsystemet NXP i.MX 8X security controller (SECO) hanterar en dedikerad Arm Cortex-M0+-processor säkerhetsoperationer, som bygger på en privat nyckelbuss och flera hårdvarumoduler för säker lagring, kryptografiacceleration och autentiserad åtkomst till debugging. (Bildkälla: NXP Semiconductors)

Utöver dessa centrala säkerhetsmekanismer koordinerar SECO-undersystemet säkerhetsåtgärder för manipulationsdetektering och säker debugging som sköts genom deras Authenticated Debug Module (ADM). För säker exekvering, stödjer den integrerade hårdvarusäkerhetsmodulen Cryptographic Acceleration and Assurance Module (CAAM) en komplett uppsättning säkerhetsalgoritmer inklusive symmetrisk och asymmetrisk kryptografi, hashfunktioner och en slumptalsgenerator (RNG).

I normal drift använder processorenheter, däribland SCU, AP och Digital Transport Content Protection-acceleratorn (DTCP), SECO-hopkopplingen för att komma åt CAAM-funktionaliteten via systembussen. Förutom åtkomst via CAAM-direktminnesåtkomst (DMA), kan SECO:s dedikerade Cortex-M0+-processor inte komma åt systembussen. Istället använder den skyddade interna anslutningar för att komma åt kringutrustning, säkert minne (RAM) och skrivskyddat minne (ROM) och dess speciella privata nyckelbuss.

Tillsammans med DTCP-acceleratorn spelar denna privata nyckelbuss en central roll i stödet för i.MX 8X-processorn för kryptering och dekryptering on-the-fly. Här använder säkerhetsprocessorn sina resurser för att tillhandahålla privata nycklar som behövs av enhetens Inline Encryption/Decryption Engine (IEE)-modul när den säkert läser från/skriver till krypterad lagring, utan inblandning av den begärande processorn, DMA-styrenheten eller en I/O-enhet.

SECO-subsystemet, som bygger på Arms TrustZone-teknik som är integrerad i enhetens Cortex-A35-processorer, fungerar också med SCU under den säkra boot-processen. I denna process tolkar SCU boot-inställningar, konfigurerar boot-källor och laddar boot-avbildningar till internt eller externt minne. SECO-subsystemet använder i sin tur sina kryptofunktioner för att autentisera signerade firmware-avbildningar efter att de har laddats, men innan de körs.

Skydda kritiska skärmar och styrfunktioner

Även om förmågan att bearbeta olika arbetslaster effektivt och säkert är viktigt, är möjligheten att skydda nyckelfunktioner för verksamhetskritiska applikationer, i exempelvis fordons- och industrisektorn, lika viktig. NXP:s i.MX 8X-familjen kombinerar sin behandlingskapacitet med säkerhetscertifierbara funktioner som krävs för att uppfylla dessa kritiska krav.

Processorfamiljens säkerhetsstöd är inbyggt på ett antal nivåer, med start redan från tillverkningen genom processtekniken med utarmad kisel på isolator (FD-SOI) som förbättrar systemets tillförlitlighet. Eftersom systemsäkerheten är beroende av en stabil säkerhetsgrund kan kombinationen av TrustZone-aktiverade AP, SECO-subsystemet och säkra boot-funktioner tillhandahålla den typ av tillförlitlig miljö som behövs för att motverka hot mot säkerheten.

Samtidigt bidrar förmågan att självständigt hantera tidskritiska uppgifter med användarens CM4-komplex och att lyfta över kritiska systemuppgifter till SCU- och SECO-subsystemen, till att säkerställa att verksamhetskritiska applikationsfunktioner förblir tillgängliga trots varierande processorbelastning. NXP har utökat detta koncept till stöd för uppgiftskritiska skärmar genom sin SafeAssure-teknik. Denna har en inbyggd, hårdvarustyrd display-failover-rutin som är Automotive Safety Integrity Level B (ASIL B)-klar på i.MX 8X-enheter. Med SafeAssure förses användare automatiskt med en failover-avbildning om enheten upptäcker ett dataintegritets- eller grafikprocessorfel. Denna failover-avbildning körs i bakgrunden och säkerställer att kritisk information förblir tillgänglig även när primärdisplayen misslyckas.

Stödet för säkerhetsapplikationer sträcker sig även till minnesåtkomsten i i.MX 8X-baserade system. Bland flera minnesgränssnitt med stöd, erbjuder i.MX 8X-enheter 8-bitars ECC för DDR3L-minne (Double Data Rate 3). Tillsammans med ECC i L2-cache (se figur 2 igen) stöder denna DDR3L ECC-funktion industriell säkerhetsintegritetsnivå 3 (SIL 3). I.MX 8X-arkitekturen utökar också ECC-stöd till externa flashlagringsenheter. Här tillhandahåller en integrerad Bose, Ray-Chaudhuri, Hocquenghem (BCH)-encoder och decoder-modul 62-bitars ECC som kan korrigera 2 till 20 enkelbitsfel i ett datablock som läses från dessa lagringsenheter.

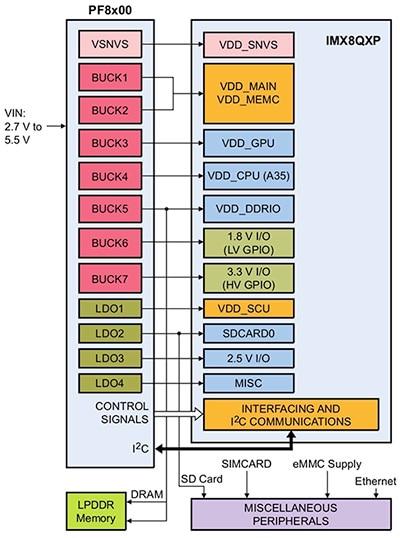

Starta upp i.MX 8X-baserade applikationer

Som med alla processorer i den här klassen kräver implementering av en i.MX 8X-baserad konstruktion noggrann uppmärksamhet åt strikta krav på strömförsörjningen, inklusive kritiska sekvenser under uppstart. För att starta i.MX 8X-enheter krävs att strömsättning sker i sekvens eller samtidigt till upp till fyra olika försörjningsgrupper, med start i SVNS-subsystemet och sedan till SCU, I/O och minnesgränssnitt och slutligen resten av enheten. Utvecklare kan enkelt uppfylla detta krav med hjälp av NXP:s PF8x00 PMIC-enheter (Power Management Integrated Circuit), som ger en komplett uppsättning spänningsreferensnivåer och styrsignaler som behövs för att stödja i.MX 8X-processorer, samt externt minne och typisk systemutrustning (Figur 5) .

Figur 5: NXP PF8x00 PMIC-enheter ger en komplett uppsättning referensnivåer och styrsignaler som behövs för att driva i.MX 8X-processorer. (Bildkälla: NXP Semiconductors)

Figur 5: NXP PF8x00 PMIC-enheter ger en komplett uppsättning referensnivåer och styrsignaler som behövs för att driva i.MX 8X-processorer. (Bildkälla: NXP Semiconductors)

När utvecklare vill implementera sina egna i.MX 8X-baserade mönster, kan de använda NXPMC33PF8100CCES PMIC som är förprogrammerad för att användas med 8QuadXPlus-processorer som MIMX8QX6AVLFZAC. Andra PF8x00-varianter, somMC33PF8100A0ES ochMC33PF8200A0ES, stödjer i.MX 8X-processorer men är inte förprogrammerade.

För säkerhetsapplikationer har modulerna i PF8200-serien - såsom MC33PF8200A0ES - funktioner integrerade som är utformade för att stödja ASIL B-system. Tillsammans med flera interna monitorer, inklusive en utgångsspänningsmonitor med en dedikerad bandgapreferens, inkluderar PF8200-PMIC:ar en felsäker utgångspinne (FSOB), som är utformad för att hålla systemet i ett säkert tillstånd under uppstart eller under ett strömavbrott. Dessutom testar en analog inbyggd självtest-rutin (ABIST) alla spänningsmonitorer medan en självtestrutin verifierar andra produktfunktioner.

Även om PF8x00 PMIC:ar kan förenkla maskinvarukonstruktion för i.MX 8X-baserade system, kan vissa utvecklare omedelbart behöva börja utvärdera i.MX 8X-enheter och snabbt prototypbygga i.MX 8X-baserade applikationer. NXP:s MCIMX8QXP-CPU i.MX 8X Multisensory Enablement Kit (MEK) ger en färdig utvecklingsplattform som kombinerar en NXP i.MX 8QuadXPlus-processor, NXP F8100 PMIC, 3 Gbyte RAM, 32 Gbyte inbäddat Multi-Media Controller-minne (eMMC) och 64 Mbyte flashminne. Tillsammans med skärm-, kamera- och ljudgränssnitt innehåller MEK-kortet en uppsättning sensorer som vanligtvis används i fordons- eller industriapplikationer. För ytterligare anslutnings-, ljud- och expansionsalternativ kan utvecklare också lägga till NXP:s MCIMX8-8X-BB-baseboard som tillval.

Slutsats

För ett allt större antal applikationer inom fordonssektor, industri, byggnadsstyrning/-övervakning och datorgränssnitt har belastningen på processor utvidgats till att omfatta både traditionell I/O-processning i realtid och och allt mer processning på applikationsnivå med multimediagrafik. Även om det finns utvecklingsalternativ för alla typer av arbetslaster, finns få tillgängliga lösningar som uppfyller det växande behovet av högpresterande, energieffektiva lösningar som kan tillgodose kraven på säkerhetscertifierbara konstruktioner till fordons- och industriapplikationer.

Som vi har visat kan utvecklare med hjälp av en familj av flerkärniga processorer från NXP Semiconductors effektivare implementera konstruktioner som uppfyller dessa olika krav och enkelt kan skalas upp för att klara nya krav på hög prestanda.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.