Hur man använder FPGA-systemkretsar i säkra och anslutna hårdvarusystem i realtid

Bidraget med av DigiKeys nordamerikanska redaktörer

2023-02-16

FPGA:er (Field programmable gate arrays), Linux-kapabla RISC-V-microcontrollerdelsystem (MCU), avancerade minnesarkitekturer och högeffektiva kommunikationsgränssnitt är viktiga verktyg för konstruktörer. Detta gäller särskilt för konstruktörer av säkra uppkopplade system, säkerhetskritiska system och ett brett spektrum av deterministiska hårdvarusystem i realtid, som t.ex. artificiell intelligens (AI) och maskininlärning (ML).

Integrationen av dessa olika delar till ett säkert, anslutet och deterministiskt system kan dock vara en utmanande och tidskrävande verksamhet, liksom att förlägga höghastighetsförbindelserna för de olika systemdelarna. Konstruktörer måste inkludera en minneshanteringsenhet, en minnesskyddsenhet, en säker startfunktion och transceivers i gigabit-klass för höghastighetsanslutning. Konstruktionen kommer att kräva aktiv och statisk strömhantering och styrning av strömrusningar. Vissa konstruktioner kommer att kräva drift inom det utökade kommersiella temperaturintervallet från 0 °C till +100 °C övergångstemperatur (TJ), medan system i industriella miljöer måste fungera vid TJ från -40 °C till +100 °C.

För att hantera dessa och andra utmaningar kan konstruktörer vända sig till FPGA-systemkretsar (SoC) som kombinerar låg strömförbrukning, värmeeffektivitet och säkerhet av försvarsklass för smarta, uppkopplade och deterministiska system.

Artikeln granskar arkitekturen för en sådan FPGA-systemkrets och hur den stödjer effektiv design av anslutna och deterministiska system. Därefter presenterar den kortfattat riktvärden för processorkraft kontra strömförbrukning för EEMBC CoreMark-Pro, tillsammans med en bild av riktvärdesprestanda för en representativ FPGA-systemkrets Artikeln beskriver hur säkerheten integreras i dessa FPGA-systemkretsar och beskriver exemplariska FPGA-systemkretsar från Microchip Technology, tillsammans med en utvecklingsplattform för att skynda på konstruktionsprocessen. Den avslutas med en kort lista över expansionskort från MikroElektronika som kan användas för att implementera en rad olika kommunikationsgränssnitt likväl som funktioner för GNSS-positionering (Global Navigation Satellite System).

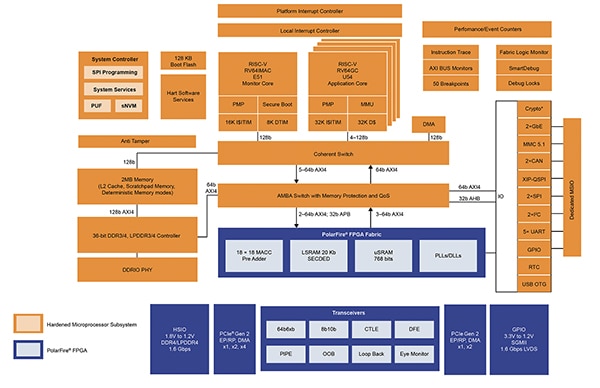

Systemkretsar tillverkade med FPGA-struktur

"Kretsen" för denna systemkrets är FPGA-struktur som innehåller systemets delar, från FPGA:n till RISC-V MCU-delsystemet som är byggt med härdad FPGA-logik. MCU-delsystemet innehåller ett fyrkärnigt RISC-V MCU-kluster, en RISC-V-monitorkärna, en systemstyrningsenhet och ett deterministiskt minnesdelsystem på nivå 2 (L2). FPGA:n i systemkretsarna innehåller upp till 460 K logikelement, upp till 12,7 gigabit per sekund (Gbps) transceivrar och andra in-/utgångsblock, inklusive GPIO (in-/utgångar för allmänt bruk) och PCIe 2 (Peripheral Component Interconnect Express). Den övergripande arkitekturen är konstruerad för tillförlitlighet. Den innehåller korrigering av enkelfel och avkänning av dubbelfel (SECDED) för alla minneskretsar, differentiell effektanalys (DPA), fysiskt minnesskydd och 128 kilobit flashstartminne (figur 1).

Figur 1: Alla element i FPGA-systemkretsen, inklusive RISC-V-delsystemen, implementeras i FPGA-strukturen. (Bildkälla: Microchip Technology)

Figur 1: Alla element i FPGA-systemkretsen, inklusive RISC-V-delsystemen, implementeras i FPGA-strukturen. (Bildkälla: Microchip Technology)

Microchip erbjuder sitt Mi-V-ekosystem (uttalas "my five") med verktyg och konstruktionsresurser från tredje part för att stödja implementationen av RISC-V-system. Den är tillverkad för att skynda på införandet av arkitekturer med instruktionsuppsättningar för RISC-V (ISA) för härdade RISC-V-kärnor och för mjuka RISC-V-kärnor. Delar av ekosystemet Mi-V ger tillgång till:

- Licenser för immateriella rättigheter (IP)

- Hårdvara

- Operativsystem och mellanprogram

- Felsökare, kompilatorer och konstruktionstjänster

De härdade RISC-V MCU:erna i FPGA-systemkretsen innehåller flera felsökningsfunktioner, t.ex. ett passivt AXI-gränssnitt (Advanced Extensible Interface) som kan konfigureras under körning och instruktionsspårning. AXI gör det möjligt för konstruktörer att övervaka den data som skrivs till eller läses från olika minnen och att veta när de skrivs eller läses.

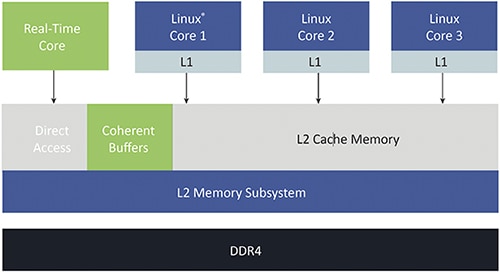

RISC-V MCU-delsystemet använder en femstegs pipeline med ett enda steg, i ordningsföljd. Den är inte sårbar för Spectre- eller Meltdown-sårbarheter som kan drabba arkitekturer med oordnade strukturer. Alla de fem MCU:erna hänger samman med minnesdelsystemet och har stöd för en blandning av deterministiska asymmetriska multibearbetningssystem (AMP) i realtidsläge och Linux. Delsystemet RISC-V har bland annat följande kapacitet (figur 2):

- Kör Linux och hårdvaruåtgärder i realtid

- Konfigurera L1 och L2 som deterministiskt minne

- Delsystem med DDR4-minnen

- Inaktivera/aktivera förgreningsförutsägelser

- Drift av pipeline i ordningsföljd

Figur 2: RISC-V-delsystemet omfattar flera processor- och minneselement. (Bildkälla: Microchip Technology)

Figur 2: RISC-V-delsystemet omfattar flera processor- och minneselement. (Bildkälla: Microchip Technology)

Mer bearbetning med mindre energi

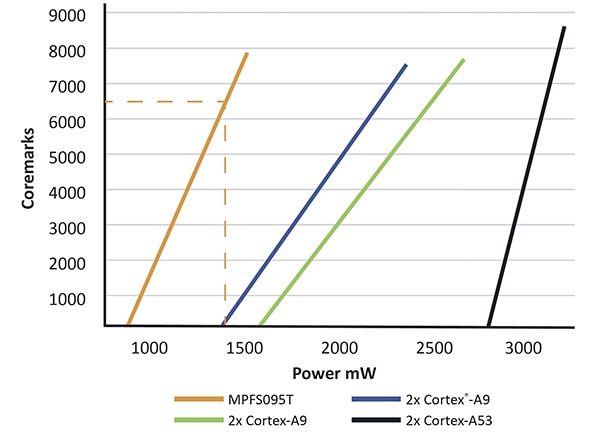

Utöver fördelarna med systemdriften, inklusive stöd för hårdvarubearbetning i realtid, är dessa FPGA-systemkretsar mycket energieffektiva. Testvärden för EEMBC CoreMark-PRO är en branschstandard för att jämföra effektiviteten och prestandan hos MCU:er i inbyggda system. Det har särskilt utformats för att mäta hårdvarans prestanda och ersätta jämförelsetestet Dhrystone.

Arbetsbelastningarna i CoreMark-PRO omfattar en mängd olika prestandakrav, parallellitet på instruktionsnivå och minnesanvändning baserat på fyra arbetsbelastningar med decimaler, samt fem vanliga arbetsbelastningar med heltal. Arbetsbelastningen med decimaler omfattar en rutin för linjär algebra som hämtats från LINPACK, en snabb Fourier-transformering, en algoritm för utvärdering av mönster i neurala nät och en förbättrad version av riktvärdet med Livermore-slingor. JPEG-komprimering, en XML-tolk, ZIP-komprimering och en 256-bitars säker hash-algoritm (SHA-256) utgör grunden för arbetsbelastningarna med heltal.

Modellen MPFSO95T av dessa systemkrets-FPGA:er, som MPFS095TL-FCSG536E, kan leverera upp till 6 500 Coremarks vid 1,3 W (figur 3).

Figur 3: FPGA-systemkretsen MPFS095T (orange linje) levererar 6500 Coremarks vid 1,3 W. (Bildkälla: Microchip Technology)

Figur 3: FPGA-systemkretsen MPFS095T (orange linje) levererar 6500 Coremarks vid 1,3 W. (Bildkälla: Microchip Technology)

Säkerhetsöverväganden

De säkerhetskritiska och hårdvarubaserade realtidstillämpningarna för dessa FPGA-systemkretsar kräver stark säkerhet utöver hög energieffektivitet och kraftfull bearbetningskapacitet. De grundläggande säkerhetsfunktionerna i dessa FPGA-systemkretsar omfattar differentiell strömanalys (DPA), resistent bitströmsprogrammering, en äkta slumptalsgenerator (TRNG) och en funktion för att göra fysisk kloning omöjlig (PUF). De omfattar även standardiserad och användardefinierad säker start, skydd av fysiskt minne som ger begränsningar av minnesåtkomst relaterat till maskinens behörighetstillstånd, inklusive maskin-, supervisor- eller användarlägen, och immunitet mot Meltdown- och Spectre-attacker.

Säkerheten börjar med en säker hantering av leveranskedjan, inklusive användning av hårdvarusäkerhetsmoduler (HSM) vid testning och kapsling av kretsen. Användning av ett 768-byte digitalt signerat x.509 FPGA-certifikat som är inbäddat i varje FPGA-systemkrets bidrar till att säkra leveranskedjan.

Ett stort antal kretsbaserade manipulationsdetektorer ingår i dessa FPGA-systemkretsar för att garantera säker och tillförlitlig drift. Om manipulering upptäcks utfärdas en manipuleringsflagga som gör det möjligt för systemet att reagera vid behov. Några av de tillgängliga manipulationsdetektorerna är:

- Spänningsmätare

- Temperatursensorer

- Detektorer för klockglidning och klockfrekvens

- Aktiv JTAG-detektor

- Aktiv mesh-detektor

Säkerheten garanteras ytterligare med AES256, motåtgärder mot kraftattacker mot symmetriska blockchifferkorrelation (CPA), integrerade kryptografiska digestfunktioner för att säkerställa dataintegritet, integrerad PUF för nyckellagring och nollställningsfunktioner för FPGA-strukturen och alla minnen på kretsen.

Exempel på FPGA-systemkretsar

Microchip Technology kombinerar dessa funktioner och tekniker i sina PolarFire FPGA-systemkretsar med flera hastighetsnivåer, temperaturklassificeringar och olika kapslingsstorlekar för att stödja konstruktörernas behov av ett brett utbud av lösningar med mellan 25 K och 460 K logikelement. Fyra temperaturklasser finns (alla med TJ-klassificering): 0 °C till +100 °C i det utökade kommersiella området, -40 °C till +100 °C i det industriella området, -40 °C till +125 °C i fordonsområdet och -55 °C till +125 °C i det militära området.

Konstruktörer kan välja mellan enheter med standard hastighetsklass eller enheter med -1 hastighetsklass som är 15 % snabbare. Dessa FPGA-systemkretsar kan drivas med 1 V för lägsta strömförbrukning eller med 1,05 V för högre prestanda. De finns i olika storlekar, bland annat 11 x 11 mm, 16 x 16 mm och 19 x 19 mm.

För tillämpningar som kräver utökad drift vid kommersiell temperatur, standardhastighet och 254 K-logikelement i en kapsling på 19 x 19 mm kan konstruktörerna använda MPFS250T-FCVG484EES. För enklare lösningar som kräver 23 K logikelement kan konstruktörer använda sig av MPFS025T-FCVG484E, som också har utökad kommersiell temperatur och standardhastighetsnivå i en kapsling på 19 x 19 mm. MPFS250T-1FCSG536T2 med 254 K logikelement är utformad för högeffektiva fordonssystem och har ett driftstemperaturområde från -40 till 125 °C och en hastighetsklass på -1 för en 15 % snabbare klocka, i en kompakt kapsling på 16 x 16 mm med 536 kulor och 0,5 mm kulavstånd (figur 4).

Figur 4: MPFS250T-1FCSG536T2 för fordonstemperatur levereras i en kapsling på 16 x 16 mm med 536 kulor och ett kulavstånd på 0,5 mm. (Bildkälla: Microchip Technology)

Figur 4: MPFS250T-1FCSG536T2 för fordonstemperatur levereras i en kapsling på 16 x 16 mm med 536 kulor och ett kulavstånd på 0,5 mm. (Bildkälla: Microchip Technology)

Utvecklingsplattform för FPGA-systemkretsar

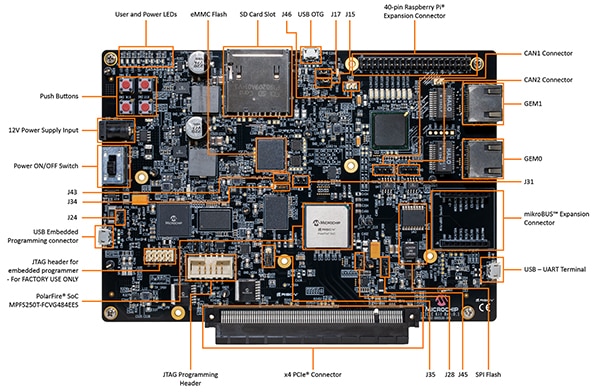

För att påskynda konstruktionen av system med PolarFire FPGA-systemkretsen erbjuder Microchip Icicle-satsen MPFS-ICICICLE-KIT-ES för systemkretsen PolarFire som gör det möjligt att utforska det femkärniga Linux-kapabla RISC-V-mikroprocessordelsystemet med låg energiförbrukning och realtidskörning. Paketet innehåller en kostnadsfri licens för Libero Silver som behövs för att utvärdera konstruktioner. Det har stöd för programmerings- och felsökningsfunktioner i ett enda språk.

Dessa FPGA-systemkretsar stöds av utvedklingssatsen för acceleratorprogram (SDK) VectorBlox som möjliggör AI-/ML-tillämpningar med låg effekt och litet format. Tyngdpunkten ligger på att förenkla konstruktionsprocessen så att konstruktörer inte behöver ha någon tidigare erfarenhet av FPGA-design. VectorBlox accelerator-SDK gör det möjligt för utvecklare att programmera energieffektiva neurala nätverk med hjälp av C/C++. Icicle-satsen har många funktioner för att tillhandahålla en omfattande utvecklingsmiljö, inklusive ett sensorsystem för flera matningsspänningar för övervakning av de olika strömdomänerna, PCIe-rotport och inbyggda minnen - inklusive LPDDR4, QSPI och eMMC Flash - för att köra Linux och Raspberry Pi samt utökningsbussar för mikroBUS för en mängd kabelanslutna och trådlösa anslutningsalternativ, samt funktionstillägg som kapacitet för GNSS-positionering (figur 5).

Figur 5: Den här omfattande utvecklingsmiljön för FPGA-systemkretsar har anslutningar för Raspberry Pi (överst till höger) och utökningskort för mikroBUS (nederst till höger). (Bildkälla: Microchip Technology)

Figur 5: Den här omfattande utvecklingsmiljön för FPGA-systemkretsar har anslutningar för Raspberry Pi (överst till höger) och utökningskort för mikroBUS (nederst till höger). (Bildkälla: Microchip Technology)

Utökningskort

Några exempel på utökningskort för mikroBUS är:

MIKROE-986, för att lägga till en anslutning till en CAN-buss med hjälp av ett seriellt perifert gränssnitt (SPI).

MIKROE-1582, för gränssnitt mellan MCU:n och en RS-232-buss.

MIKROE-989, för anslutning till en kommunikationsbuss med RS422/485.

MIKROE-3144 har stöd för LTE Cat M1- och NB1-teknik som möjliggör tillförlitlig och enkel anslutning av 3GPP IoT-enheter.

MIKROE-2670 möjliggör GNSS-funktioner med samtidig mottagning av GPS- och Galileo-konstellationerna plus BeiDou eller GLONASS, vilket ger hög positionsnoggrannhet i situationer med svaga signaler och/eller störningar i urbana raviner.

Sammanfattning

Konstruktörer kan använda sig av FPGA-systemkretsar när de utvecklar uppkopplade, säkerhetskritiska och deterministiska hårdvarusystem i realtid. FPGA-systemkretsar tillhandahåller ett stort utbud av systemelement, inklusive en FPGA-struktur, RISC-V MCU-delsystem med högeffektiva minnen, kommunikationsgränssnitt för hög hastighet och många säkerhetsfunktioner. För att hjälpa konstruktörerna att komma igång finns det utvecklingskort och miljöer som innehåller alla nödvändiga delar, inklusive utökningskort som kan användas för att implementera ett stort antal kommunikations- och lokaliseringsfunktioner.

Rekommenderad läsning

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.