Skydda integriteten för sensordata genom att använda självidentifiering och diagnostik

Bidraget med av DigiKeys nordamerikanska redaktörer

2019-03-29

Sensorteknik och Sakernas internet (IoT) ökar påtagligt sin närvaro i industriella, kommersiella och konsumentrelaterade sammanhang. Samtidigt med denna expansion ökar behovet konstant av att skydda integriteten för data som kommer från de relaterade sensorerna och deras frontend-gränssnittskretsar.

Det potentiella problemet med dataintegritet blir ännu allvarligare när en enda gränssnitts-IC har stöd för flera sensorer, eftersom problem med en enda IC kan orsaka ett helt kluster med korrupta avläsningar. Detta kan i sin tur leda till en felaktig bedömning av sensorsituationen, vilket kan innebära olämpliga eller till och med farliga systemåtgärder.

Det här artikeln undersöker de olika källorna till både hårda och mjuka (övergående) fel och felaktiga sensoravläsningar i signalkedjan från sensor till processor. Sedan kommer den att presentera en mycket integrerad IC från Analog Devices och visa hur dessa problem kan hanteras med diagnostik av själva sensorerna och deras digitala I/O.

Signalbanan sensor-till-processor

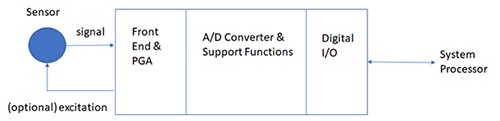

De faktorer som i slutändan påverkar integriteten för alla sensoravläsningar börjar med de tre huvudfunktionsblocken i signalbanan som visas på bild 1. Dessa block är:

- Sensorn och dess ledningar

- Den analoga klientdelen i signalbehandlings-IC, centrerad på analog-till-digitalomvandlaren (ADC)

- Digital I/O till systemprocessor

Figur 1: Den grundläggande signalbanan sensor-till-processor består i huvudsak av några grundläggande funktioner, men ett praktiskt och användbart gränssnitts-IC ger ytterligare funktioner. (Bildkälla: DigiKey)

I ett flerkanalssystem utgörs sensorerna ofta en blandning av olika typer av termoelement, resistanstemperaturdetektorer (RTD:er) och trycksensorer. Ett sensorfel kan uppstå eller så kan dess sammankopplingsledningar öppna eller kortslutas till en anslutande ledning, strömlinje eller jordning.

Beroende på sensortypen kan ett fel i dess ledningar omedelbart uppenbara sig eftersom avläsningen hamnar ”utanför skalan”. Som kontrast till detta kan vissa fellägen leda till felaktiga signaler som ser ut att vara korrekta. Vissa sensorer, som RTD:er, behöver en extern stimuleringsström och den här strömmen måste ligga inom ett visst intervall för giltiga avläsningar. Av dessa anledningar är det en bra idé att testa kontinuiteten för signalbanan mellan sensorn och den analoga klientdelen och även kontrollera att signalen fortsatt ligger inom den tillåtna lägsta och högsta gränsen, helst genom att använda en analog krets som är oberoende av möjliga ADC-problem.

Det ger inte bara korrekta avläsningar utan även avläsningar på vilka systemets beslutsfattande algoritmer kan köras med en mycket hög tillförlitlighet för källdata.

Alla dessa extra kontroller ökar dock behovet av extra komponenter, ger större avtryck och kräver extra designtid.

Självidentifierande IC säkerställer integritet för sensordata

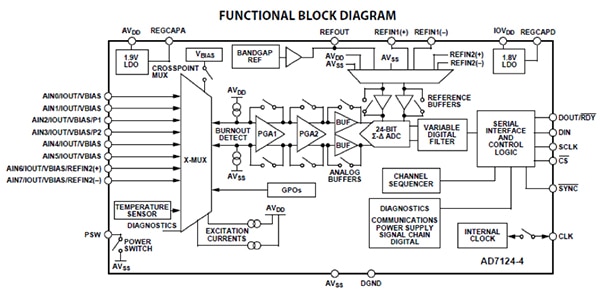

För att hantera behovet av hög dataintegritet med så liten påverkan som möjligt på designtid och avtryck, har Analog Devices lanserat AD7124-8BCPZ-RL7, ett sensorfokuserat ADC och gränssnitt som går mycket längre än grundläggande signalbehandling och -omvandling. Produkten innehåller flera funktioner för signal- och självdiagnosticering som säkerställer dataintegritet.

Figur 2: AD7124 sensorfokuserat ADC och gränssnitt går mycket längre än grundläggande signalbehandling och -omvandling med flera funktioner för signal- och självdiagnosticering för att säkerställa dataintegritet. (Bildkälla: Analog Devices)

AD7124 är en enhet med fyra kanaler, låg ljudnivå, låg effekt, 24 bitar och sigma-delta (Σ-Δ). Samplingsfrekvensen går från 1 sampling/sekund, som duger för flera sensorklasser och deras tillämpningar, upp till 19 200 samplingar/sekund. Vid den lägsta samplingsfrekvensen krävs 255 mikroampere (μA). Noggrannheten i avläsningarna på enheten förbättras av designens betoning av låga ljudnivåer, under 25 nanovolt (nV) rms och den låga förskjutningen av dess interna referensspänning (10 ppm/°C).

AD7124 är tillgänglig i paket med 32-ledningars LFCSP och 24-ledningars TSSOP. En flexibel digital I/O har stöd för 3- och 4-tråds SPI, QSPI, MICROWIRETM och DSP-kompatibla gränssnitt.

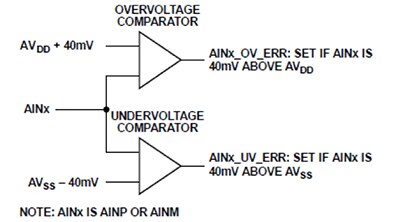

AD7124 hanterar de ledningsproblem för sensorn som nämnts tidigare med två tekniker: signalgränslarm och burnout-ström. Signalgränslarm använder ett överspännings-/underspänningslarm för att kontrollera den absoluta spänningen på vart och ett av de fyra paren med analoga inmatningskontakter (figur 3). Den här spänningen måste vara inom ett definierat fönster för att uppfylla specifikationerna i databladet.

Figur 3: En grundläggande verifiering av sensorledningar med signalgränslarmen använder hårdvarubaserade komparatorer med fasta lägsta/högsta inställningar. (Bildkälla: Analog Devices)

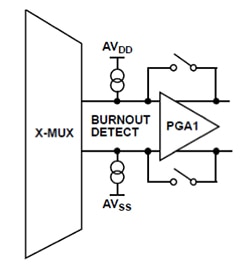

Burnout-ström använder ett par med kompletterande programmerbara strömsänkor och -källor. Med hjälp av strömsänka/-källa för ett fördefinierat par med strömmar till sensorn kan AD7124 verifiera deras integritet (figur 4). Strömmarna, som antingen är helt på eller av, växlas till det valda analoga inmatningstrådparet under testet.

Figur 4: Med hjälp av strömsänka/-källa för ett fördefinierat par med strömmar till sensorn kan AD7124 verifiera deras integritet. (Bildkälla: Analog Devices)

En fullskalig avläsning (eller nästan) kan innebära att frontend-sensorn är en öppen krets. Om den uppmätta spänningen är 0 volt kan det tyda på att strömomvandlaren har kortslutits. Motsvarande flaggbit ställs in i felregistret för att indikera förekomsten och typen av fel.

I tillämpningar där användaren tillhandahåller den externa referensen istället för att använda den interna referensen, vilket ofta görs med RTD:er eller töjningsgivare, kontrollerar AD7124 att alla referensspänningar för externa omvandlingar är korrekta.

Verifiera frontend och ADC

Även om externa sensorer och deras ledningar är den troligaste källan till problem är det avgörande att verifiera prestanda hos varje frontend-/omvandlings-IC. Funktioner som kan vara utanför specifikationerna eller fungera felaktigt är:

- Den interna ADC-spänningsreferensen

- Den programmerbara förstärkaren (PGA) som förstärker inmatningssignalen för att matcha ADC-spannet för den högsta upplösningen

- LDO (low-dropout regulator) som levererar den sensorimpuls som krävs

- Interna strömskenor för IC

- Självtest av ADC

För att testa den analoga delen av signalbanan anropar AD7124 självtest baserade på hårdvaran och den fasta programvaran. Det genererar en signal på 20 millivolt (mV) som kan anslutas internt till någon av dess fyra differentialingångskanaler och sedan digitaliseras. Detta uppfyller flera syften: det verifierar den grundläggande driften för ingångskanalens multiplexer och ADC; det möjliggör även utvärdering av PGA genom att byta PGA:s förstärkningsinställningar och kontrollera de resulterande ADC-avläsningarna.

ADC-enheten kan också vara en källa till möjliga problem. AD7124 använder den väletablerade Σ-Δ-omvandlararkitekturen med sin 1-bitars modulator och nödvändiga digitala filter. Vid en komplett testning av ADC-prestanda används både analoga och digitala tekniker.

Om modulatorutmatningen i AD7124 innehåller 20 ettor eller nollor i rad, tyder det på att modulatorn har mättats till endera skenan, och en felflaggbit sätts. IC kontrollerar dessutom att ADC-förskjutningskoefficienten är mellan 0x7FFFF och 0xF80000 efter dess självstartade förskjutningskalibrering. Om den är utanför detta intervall sätts en annan felflaggbit. Under en fullskalig kalibrering sätter slutligen alla överströmmar av det digitala filtret en annan felflaggbit.

Interna och externa strömkällor och skenor är också potentiella problemkällor. Många sensorer kräver en liten mängd exiteringsström och denna tillhandahålls ofta av en liten och tyst LDO inuti den analoga fronten-IC.

AD7124 kontrollerar sina LDO-utmatningar på två sätt. För det första kan utmatning från LDO dirigeras internt till ADC och jämföras med det förväntade värdet. För det andra övervakar en hårdvarukomparator som är oberoende av ADC kontinuerligt LDO mot IC-referensen. Om det faller under ett visst gränsvärde sätts en felflaggbit. Det innebär att LDO kan bedömas under initieringen och detta kan även ske kontinuerligt utan att konstant förbruka processorresurser.

För ytterligare säkerhet kan testkretsen som användas för att övervaka tillförseln kontrolleras (i viss utsträckning) genom att dess inmatning ansluts till jord (nominellt 0 volt). Därefter görs en kontroll av den digitala avläsningen. AD7124 säkerställer dataskyddet ytterligare genom att kontrollera att de frånkopplingskondensatorer på 0,1 mikrofarad (µF) som krävs är på plats och anslutna. Detta sker genom att AD7124 dirigeras att fysiskt koppla från frikopplingskondensatorn genom den interna brytaren och sedan kontrollera LDO-utmatningen. Om LDO-spänningen faller är frikopplingskondensatorn elektriskt frånvarande. Återigen sätts en felflaggbit.

Givetvis har alla IC en maximal temperaturklassning, som vid överskridande leder till att specifikationerna ej hålls eller att ett fel uppstår. Därför är en sensor inbyggd i alla AD7124 för att insatstemperaturen ska kunna läsas av när som helst, med en typisk noggrannhet på ±0,5 °C.

Vad gäller för digitala fel?

Så här långt har vi tittat på att säkerställa prestanda och noggrannhet med avseende på den analoga sensorn eller konverteringsfunktioner. I elektriskt krävande industrimiljöer där flera av dessa sensorer driftsätts finns dock problem med buller, EMI/RFI och transienter som påverkar digital elektronik. Därför är det viktigt att säkerställa prestanda för den interna digitala kretsen, samt gränssnittslänken till systemprocessorn, för att säkerställa stabilitet för data samt alla läsa-/skrivåtgärder.

AD7124 uppnår detta genom en mångsidig metod som inleds med följande åtgärder och funktioner:

- Prestanda för masterklockan kontrolleras. Masterklockan behövs för att sätta utdatafrekvens, filterinställningstid och filterhackfrekvenser. Den kontrolleras av ett oberoende uppräkningsregister som kan läsas tillbaka när som helst.

- Antalet SCLK-pulsslag som används i varje SPI-läs- eller skrivåtgärd kontrolleras via en speciell klockräknare. Antalet ska vara en multipel med åtta (alla SPI-åtgärder använder 8, 16, 32, 40 eller 48 klockslag).

- AD7124 kontrollerar att läs- och skrivåtgärder endast riktas till giltiga registeradresser.

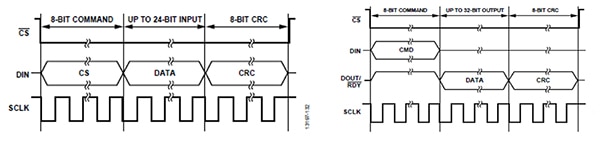

Dessa steg uppfyller kraven på de interna åtgärderna men säkerställer inte integriteten för processorgränssnittet och dess data. För att ge mycket hög tillförlitlighet i data kan användaren anvisa AD7124 att implementera en algoritm med cyklisk redundanskontroll (CRC) och polynom kontrollsumma. Kontrollsumman ser till att endast giltiga data skrivs till ett register och tillåter validering av dataläsning från ett register (figur 5). Observera att kontrollsummor är en pålitlig teknik för att identifiera enkelbitsfel men att den inte kan korrigera dem.

Figur 5: En polynom CRC-kontrollsumma läggs till i (vänster) SPI-skriv- och (höger) SPI-lästransaktioner för identifiering av enkelbitsfel. (Bildkälla: Analog Devices)

När det aktiveras beräknar den åtgärden en kontrollsumma för datablocket och bifogar den till varje ände av läs- och skrivtransaktionen. För att säkerställa att registerskrivningen lyckades måste registret läsas tillbaka för att bekräfta den lagrade kontrollsumman mot den som beräknats från data.

I en elektriskt krävande miljö kan till och med minne få bitfel. För att få en kontroll på hög nivå mot sådana fel i register på chipp beräknar AD7124 kontrollsumman för en mängd åtgärder varje gång:

- Det här är en skrivcykel för register

- Det finns en förskjutningskalibrering/fullskalig kalibrering.

- Enheten utför en enda konverteringscykel och ADC-enheten övergår i standby-läge efter att konverteringen har slutförts

- Läget för kontinuerlig läsning avslutas

För ökad stabilitet utvärderas även det interna läsminnet (ROM). Vid start initieras alla register till standardvärden som lagras i ROM. En CRC-beräkning utförs på ROM-innehållet vid start. Det skiljer sig från det lagrade CRC-resultatet och tyder på ett fel i minst en bit.

AD7124 ger även exitering för flera typer av sensorer, samt signalkonditionering och skalning av sensorutsignalen genom förstärkare och en PGA. Denna enastående stabilitet skapas genom att enheten har flera interna register för initiering som etablerar önskade funktionslägen och -parametrar och flaggar diverse fel.

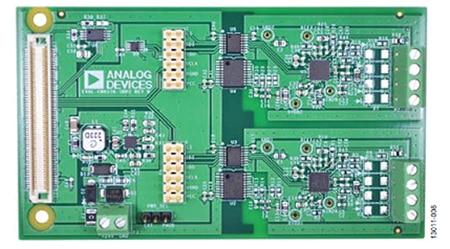

Använd AD7124-utvärderingskort till att snabbstarta designarbeten med AD7124

AD7124 är ett avancerat system med många designmöjligheter och stor prestandakapacitet. Det är inte en okomplicerad sensorgränssnitts-IC som bara behöver sättas fast. I utbildningssyfte och som en hjälp till konstruktörer att snabbt bekanta sig med dess möjligheter tillhandahåller Analog Devices även utvärderingskortet EVAL-CN0376-SDPZ (figur 6).

Figur 6: Utvärderingskortet EVAL-CN0376-SDPZ underlättar designarbetet och ger full tillgång till flera av funktionerna i AD7124. (Bildkälla: Analog Devices)

Utvärderingskortet innehåller kraftförsörjningen och de externa komponenter som behövs för att ansluta AD7124 till en rad faktiska sensorer samt en processor. Det stöds av en Windows PC-baserad CN-0376-utvärderingsprogramvara som kommunicerar genom en USB-port för att konfigurera och samla in data från utvärderingskortet.

Slutsatser

Många avgörande beslut fattas av avancerade algoritmer som är inbäddade i systemprocessorer, nu ofta förstärkta med artificiell intelligens (AI). Det är viktigare än någonsin att de rådata som algoritmerna använder sig av för slutsatser och åtgärder är tillförlitliga. IC:er som AD7124 ökar tillförlitligheten i data i flera steg, och ser till att varje länk i signalbanan, från ledningar och sensorgränssnittet till den egna prestandan och de egna funktionerna, fungerar som förväntat och inte är korrumperade.

Disclaimer: The opinions, beliefs, and viewpoints expressed by the various authors and/or forum participants on this website do not necessarily reflect the opinions, beliefs, and viewpoints of DigiKey or official policies of DigiKey.